### **OCCASION**

This publication has been made available to the public on the occasion of the 50<sup>th</sup> anniversary of the United Nations Industrial Development Organisation.

#### **DISCLAIMER**

This document has been produced without formal United Nations editing. The designations employed and the presentation of the material in this document do not imply the expression of any opinion whatsoever on the part of the Secretariat of the United Nations Industrial Development Organization (UNIDO) concerning the legal status of any country, territory, city or area or of its authorities, or concerning the delimitation of its frontiers or boundaries, or its economic system or degree of development. Designations such as "developed", "industrialized" and "developing" are intended for statistical convenience and do not necessarily express a judgment about the stage reached by a particular country or area in the development process. Mention of firm names or commercial products does not constitute an endorsement by UNIDO.

#### FAIR USE POLICY

Any part of this publication may be quoted and referenced for educational and research purposes without additional permission from UNIDO. However, those who make use of quoting and referencing this publication are requested to follow the Fair Use Policy of giving due credit to UNIDO.

### **CONTACT**

Please contact <u>publications@unido.org</u> for further information concerning UNIDO publications.

For more information about UNIDO, please visit us at www.unido.org

MICROELECTRONICS TECHNOLOGY: PROBLEMS AND PERSPECTIVES IN COUNTRIES OF WEST ASIA AND NORTH AFRICA.

The paper is a result of a UNIDO sponsored mission in Iraq, Saudi Arabia UAE (Abu Dabi), Tunisia and Morocco. The author wishes to record his appreciation to the sponsors for making his trip possible, UNECWA officials for their assistance and encouragement and UNDP officers i visited countries for their help in administrative matters and for organising certain visits. Finally, the author would like to thank the members of the mission Mr Felix Hinc and Mr Hassan Charif for their excellent cooperation and many valuable discussions. The contribution of the latter deserves special mention due to his profound knowledge of the region and extensive contacts with key people in the field which were invaluable in achieving mission objectives.

The mission was conducted in November-December 1983 and this paper is based on meetings with over a 100 people in 45 organisations spread over 25 days. The organisations covered include government ministries, national computers centres, major oil and mineral companies, investment and planning institutions, academic, R & D and manufacturing organisations. Since such an exercise was being attempted for the first time coverage has been extensive in order to obtain a perspective of the status, problems and potential for microelectronics in the region. However, these notes represent impressions of a 3 week visit only, at a given period in time, with the primary objective of preparing a backgroung paper for the experts meeting in Kuwait in March 1984.

The countries in the UNECWA region and North Africa recognize both the need and potential for the application and development of microelectronics technology explicity is well ahead of the absorptive capacity of the region both in terms of infrastructure and human resources. Finance clearly is not a constraint, especially, in the oil exporting countries of the region. Consequently, the present situation does not tend toward a stable technological equilibrium and special efforts will be necessary both in terms of infrastructure development and local manufacture if the present rate of diffusion of the technology, assuming effective utilisation, is to be maintened.

We ile special efforts to develop applications of this technology have been made in the public domain, as is evident from the chain of national computers centres that have been established, there is a considerable spread in the capabilities of individual countries. Thus, CNI in Tunis and IMEG in Casablanca/Rabat seemed to be considerably ahead of their counterparts in the other countries both in terms of human resources and methodology. Greater regional cooperation with the assistance of UNECWA/UNICO between these institutions could go a long way in not only rectifying the imbalance but further upgrading capabilities.

In terms of industrial applications, the largest market for microprocessors based control systems was the oil production/exploration and mineral extraction/purification sectors. Thus, while ARANCO, Saudi Arabia the largest oil exploration/production company was an impenetrable fortress tied to primarily US vendors for the both hardware/software support, the situation in ADNOC, Abu Dabi, and PETROMIN, Saudi Arabia appeared relatively more flexible with greater potential for development of local capabilities to support their future

requirements for microelectronics hardware and software. Similarly, OCP, Casablanca, Morocco and probably the Jordanian Phosphate Company are fare more open and keen to use / develop local capabilities. Another application area of considerable potential for the region was in the generation, transmission and distribution of electricity and the example of STEG, Tunis deserves to be supported and emulated. Finally, the largest potential for the application of microelectronics technology is in the education and office automation sectors as brought out succinctly in the paper of W.M. Turski provided the problem of standardisation of the Arabian character set can be swiftly and unambigously resolved.

Herein also, lies an opportunity of volume manufacture of low cost bilingual terminals and microcomputers. The efforts of Saudi Arabia (Al-Farabi computers), IMEG (low cost micros for schools) and CNI (terminals) need to coalesced and catalysed effectively by UNIDO/ECWA.

The manufacturing base in both the ECWA and North Africa region is presently very limited and would have to be considerably augmented to sustain an autonomous microelectronics industry. Given the gross national product of the region and its continuously increasing requirements for microelectronics products, there is a definite need to evolve a strategy for the development/manufacture of microelectronics products/components for the region. The present efforts at TV assembly at SADA, Morocco, SONELEC, Algeria or in Tunis and Syria nor the offshore assembly of components at SNRF, Morocco of their manufacture to a limited extent at SONELEC, Algeria constitute a viable or effective strategy for the future development. In the experience of the mission, Tunis was the only country where the potential to set up local manufacture on an integrated basis was being seriously examined, primarly, by BDET and API. Thus, 3DET was talking to both Jeumont Schneider. France to establish manufacture of EPARXS (10,000 lines per year) and to COMTERM, Canada, to manufacture terminals, while API

wanted to establish of passive components i.e. resistors and capacitors. Both institutions, however, were clearly aware and concerned about the economic viability of these projects and were looking for a wider regional market.

In the author's view, exclusively national strategies cannot be pursued by individual countries in the region since the requisite combination of high per capita income and population does not simultaneanusly co-exist. On the other hand, the electronics market for the region as a whole is substantial enough to pursue an economically viable developed and growing at a significant rate. Two sectors which need to be singled out are consumer electronics and communications. While it was not possible to obtain any quantitative data on the consumer sector, the fact that production of color TV sets exceeds 100 per day in both Morocco and Algeria, each with a population of 30 millions approximately and 50,000 in Tunisia with a population of 6-7 millions, the color TV market in the ECWA + North Africa region as a whole ought to exceed 1,5 millions sets per annum. If to this is coupled the demand for VCRs, combination sets, calculators, personnal computers and electronic watches, this market is estimated to be in the neighbourhood of \$\beta\$ 2 billions.

An earlier ECWA/UNIDO study shows that the demand for telephone exchange lines is the ECWA regions is projected at 433,000 per annum during the period 1981-85 growing to 796,000 per annum between 1986-1990 with a matching demand for ECH channels. The corresponding demand for telephone sets has been estimated at 563,000 and 1,035,000, respectively. Further, the average annual investment in the regions networks has been estimated at \$886 millions (1981-85) and \$1,622 millions (1986-1990).

The estimate is based on a educated conjoncture given the GNP, population, present level of assembly and visibility of these products.

While no accurate estimates exist for the computer market in the region, Saudi Arabia alone has been importing equipment at the rate of \$ 100 million/year during 1981 and 1982. Similarly, the requirements for microelectronics, especially, microprocessor based process controls for the oil exploration/production is significant as discussed in the report of the mission. Further, standardisation of the Arabian character set could considerably stimulate the demand for micros and terminals in schools and the office, respectively.

Given the above demand, production of a range of active and passive electronic components clearly appears to be a viable proposition. In the consumer sector for the type of products indicated above, components represent almost 40-50% of the value of these products. Similarly, in the area of switching, the cost of components per line for a system like the E 10 B of CIT-ALCATEL is \$ 125/line, namely 50% of the cost per line. While clearly a more detailed study is required to accurately assess present requirements and future demand in these sectors, once this has been done, it would not be too difficult to extract a profile of component requirements both in terms of quantity and value. A pricri, it would appear that adequate demand exists for establishing a viable component industry. However, it must be recognized from the outset that such an industry would only be viable if it was established on a regional basis. Consequently, standardisation of hardware must constitute an important element of such a strategy. Clearly, the regional issues involved in an industrial strategy for microelectronics need a closer examination, which is not the purpose of this paper.

Several suggestions have been made in Turski's paper for augmenting the software capabilities in the region. A complementary set of measures to upgrade the regions "hardware" capabilities is essential if a composite and autonomous microelectronics capability is to be established. These are discussed below:

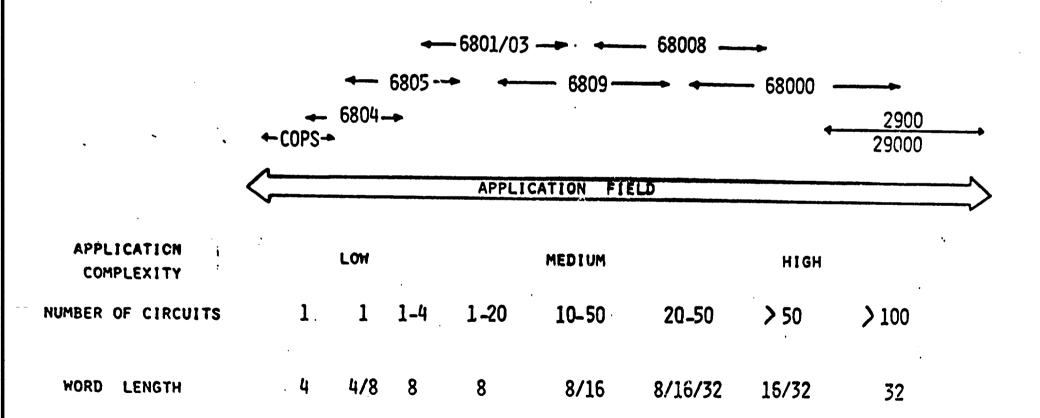

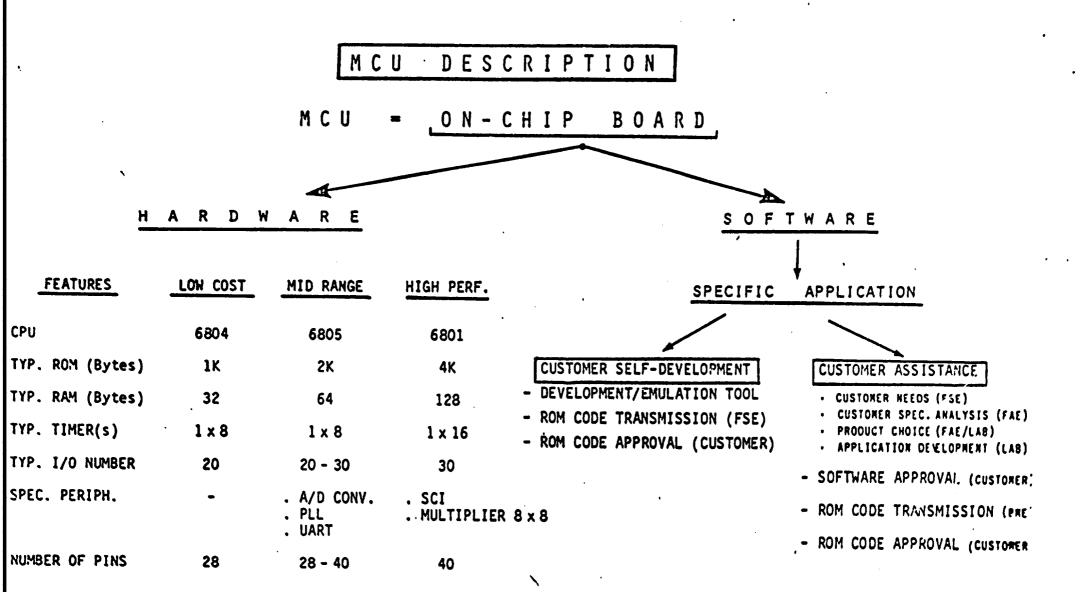

There are 2 major microprocessor families with extensive applications and software currently in vogue, namely, the 8 and 16 bit families of Intel and Motorola. The orientation of the former is primarily towards the personal computer market, and even more so after IRM's entry. Motorola's 6800 and 68 000 series on the other hand are more extensively used for industrial process control applications. The applications coverage and some of the hardware features of these series is summarized in Tables 1 and 2. There are several processor, memory, interface and controller modules together with debugging software packages and development support tools available. Several major semiconductor/system companies have thrown their support behind these series, namely, HITACHI, MOSTEK and THOMSON, thus providing the requisite back up to ensure its continued use. There is a need to establish a regional capability in systems integration around such a concept. In order to ensure effective implementation of such a concept a core group of the more willing users, partly identified above, together with a group of experts from the academic sector needs to be formed with necessary support from ECWA/UNIDO to prepare a feasibility report in terms of the regions requirements in the major application areas, i.e. on exploration/production, mineral extraction/purification and power generation/distribution, etc. Based on these findings a regional centre could be created with appropriate linkages for technology transfer both with OEM suppliers of such components and system suppliers.

The key element in any future strategy to design and build electronic systems is the ability to design the silicon "chip". All IC's technology is built on the foundation of semiconductor device physics which provides the essential knowledge is semiconductor fabrication technology which allows the designed IC's to be physically constructed and above this in turn is the body of circuit and logic design knowledge. Various areas of knowledge in the manufacture of IC's have reached different stages of development, with the higher level design skills being the least highly developed. In fact, all the evidence available strongly suggests that these traditional skills will not enough for VISI, design methodology is in essence a search for the right approach to built computer-aided engineering systems that will go on to design the IC's semi-automatically. There is a shift from hardware concepts. It appears reasonably certain that the whole area of the design of highly concurrent systems will become one of the most rapidly developing technological fields of the coming year. All these changes are likely to affect the future structure of the industry in terms of being integrated both in terms of design and fabrication as at present.

It is likely that design will become increasingly decentralised and the concept of the "silicon foundry" which does primarily fabrication develop. The emergency of the large custom and semi-custom markets in the eighties is a consequence of this change. Further, design automation systems in terms of both hardware and software in unbundled form are becoming increasingly available. The "work station" which is a low cost design system is becoming increasing viable and several of these systems are being marketed. While the concept of decentralised desgin works quite well in a "foundry" rich environment as has been demonstrated by the sucess of the "multi-project chip", in a developing

country environment it is important that local design capabilities are supported by at least a pilot level "silicon foundry" with the capability to process wafers using at least one stable technology. Obviously, local design centres could still need to have linkages with other silicon foundries in both Europe and the USA. Since the concept of the "silicon foundry" is most prevalent in the USA a list of such foundries is summarized in Table III.

A ISI design centre necessarily has 2 components, namely, hardware and software. In terms of hardware the most extensively used system by far is the VAX II/780. The system has the great advantage that most of the software packages available for ISI design can be directly implemented on it without any modifications. While it is not proposed to go into the details of the hardware configuration, the VAX II/780 uses graphic terminals which constitute the man machine interface. Depending on the configuration the hardware costs for establishing a design centre would be typically S 300,000. The design software could have to include a package for registrer level entry, a logic simulator (TEGAS, SPLICE, EPILOG), a circuit simulator, (SPICE), preferrably a processor simulator (SUPREME), an interactive graphics backage (CAIMA, GCI, etc...) a package for design rule check, a cell or element extractor from the lay out to verify or resimulate the logic, software for a PG tape output for mask fabrication and cell library with a data basis containing the requisite design rules i.e. layout and electrical. There are several vendors for such packages besides some of them are also available from universities in the USA. However, while integration of unbundled software from multiple sources is more economic it is also that much more difficult to implement. The output of a design centre

is a PG centre from which the mask set for processing the "chip" is fabricated, either using a laser pattern generator or a E-Beam machine. While several mask fabrication shops are available in the USA and Europe, if it is decided to set up a pilot "silicon foundry" for wafer fabrication, then it could also be necessary to set a mask fabrication facility.

As a first step it would be important to establish a regional design centre on a immediate basis for which requisite support should be provided by UNIDO. Such a centre should play a modal role in creating a chain of national design centres in a optimally cost-effective manner i.e. by shar. the software resources. In order to ensure synergy all national centres and the regional centre should be networked together or at least linked by electronic mail. It would then be possible to rapidly create a corps of designers in the region and thus lead to rapid diffusion of the technology. An important goal of such a programme should be software development, to upgrade the design tools and build the next generation of design automation systems.

The second level of interconnection in a electronics systems is conventionnally provided using printed circuits boards (PCB), and they tend to have 2 or more levels for professional systems. The capability to design and fabricate double sided PCBs with through hole plating was only available at SNRF, Morocco a Thomson subsidiary. Similarly, the mission did not see any evidence of the design and fabrication of hybrid circuits through here again the assembly of thick film hybrids was being done at SNRF based on imported screened substrates and other active/passive components. While the ability to design and fabricate both the above components is a essential prerequisite to built microelectronics sub-systems/systems, equally important is the ability to populate and test these sub-assemblies. A regional centre needs to be

established to fill this gap with additional important function of training personnel in these techniques from the countries of the region. Support for such a concept from existing/potential manufacturers of sub/systems needs to be sought in order to promote the above concept . Further, ECWA/UNIDO could provide the necessary technical inputs needed in planning such a facility.

The region has several excellent schools of which the Technological University, Baghdad, UPM, Saudi Arabia and ENSET and ENIT, Tunisia deserve special mention. In terms of computing capabilities UPM is clearly ahead of all other institutions visited with a VAX II/780, further gives it a head sart to establish a centre for ISI design. However, as been pointed out while considerable emphasis was being placed on the applications and software aspects of microelectronics, there was an a finite need to augment the hardware aspects of the technology i.e. materials science, semiconductor device fabrication techniques, CAD for chip design etc... In this context the approach of The Centre for Integrated Systems (CIS), Stanford University is worth emulating. CIS seeks to integrate solid state research and fabrication on the one side with applications on the other. The intention is to merge the three disciplines of the electronics age computer science, information cience and physical science. In order to make the system synergistic it is proposed that the scientists working in solid state physics will investigate the fundamental principles of IC's and pass their results to the IC's engineers. These engineers will use that knowledge to design new devices and fabrication techniques, and give them to the application engineers, who turn will define new systems and integrate the chips into complete functional systems. Concurrently, the computer and information scientists are developing the tools to design ant test the IC's and so on. The concept brings together all the composite skills and tools to solve the increasingly complex problems of tomorrow.

The communications infrastructure in the ECWA region is being developed at a rapid rate. There is a general trend to shift to electronic switching systems, as witnessed in Morocco and Tunisia. Similarly, Jordan and Egypt have opted for CIT ALCATEL'S E 10 B system which is digital with Saudi Arabia having gone in for ERICSON. The impression gained by the mission was that Saudi Arabia. UAE. Tunisia and Morocco had relatively efficient telephone networks well integrated internationally. The launching of ARABSAT in october 1984 will further augment the region's capability for intra-regional communications. Consequently, the time is ripe to start planning for a multi-service national/regional network which can transmet voice, data and video signals, with the long term goal of establishing an integrated services digital network (ISDN). In particular the development of local area networks, packet switching, electronic mail and teletext/viewdata is of special significance. The need to establish common standards for the systems hardware/software is of crucial importance for the future development of microelectronics in the region and UNIDO with assistance from ITU could assist in commisioning a feasibility study in this area for the region.

The application of microelectronics in the service sectors like education health and transportation is likely to produce the greatest social benefit. The awareness of this potential was highest in Morocco

namely, at the Centre for Arabisation, Rabat and ANIT and ENSET in Tunis. There is a need to focus these efforts into a wider regional one and the methodology suggest in Oliphant's paper, "Microprocessor Applications in Developing Countries" (UNIDO, 1982), to establish a hierarchy of microprocessor applications development centres with the requisite hardware/software tools and suitable institutional support could form an useful basis for preparing an implementation plan for the region.

The problems of equipment maintenance and the lack of availability of components spares was pointed out by several organisations. Equipment maintenance can be segregated into two categories, computers and other equipment. A specialised corporation to deal with computer maintenance has been quite successful in the indian context and a modified version of such a concept to meet regional requirements merits a cluser examination. Other electronic equipment covers a wide range and spectrum and includes analytical, measuring and medical instrumentation and its meintenance in view of the large variety of types and vendors is more difficult and no simple solution exists. The programme at ENIT, Tunis to train high level technicians for maintenance needs to be more closely analysed to determine the extent of its sucess and the need for further support and diffusion of the approach. Finally, all development programmes in the region seemed to suffer due to lack of component availability one possible solution to this problem could be to set up a regional component bank which stockpiles a list of priority components with support from ECWA/UNIDO.

MICROPROCESSOR

AND PERIPHERAL

### MICRO APPLICATION COVERAGE

⊃ S REFERENCE MANUAL

TABLE 2

|                                                                                                                                                  |                                   |                                                      |                    | num Featur                                     | res Averlab<br>re Size Gate<br>n attown in p |                                                                               |                                           |                        | Maximum<br>Production                                                                                                       | Cost Pur                                                                                                                           |                                                            |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------|--------------------|------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|

| Company<br>Contact Person                                                                                                                        | Me-G                              | WOS<br>S-G                                           | Me-G PA            | MOS<br>S-G                                     | M-G C                                        | MOS<br>Si-G                                                                   | Bipoler                                   | Prod.<br>Wuler<br>Size | Requirements<br>(S or waters<br>per year)                                                                                   | Prototype Run<br>(with prod cost,<br>If everlable)                                                                                 | Design Formet<br>from Customer                             |  |

| Acrian, Inc.<br>10000 Bubb Road<br>Cuperano, CA 95014<br>(408) 996-8522<br>Jim Huskens<br>VP of Mg.                                              | у<br>Бұлп<br>(10 <sub>9</sub> лп) |                                                      |                    |                                                | ј<br>Бµт<br>(10µт)                           |                                                                               | •                                         | 2                      | \$10,000·ye                                                                                                                 | nMOS: \$3,000<br>per 25 waters<br>CMOS: \$4,000<br>per 25 waters<br>Bipolar: \$25<br>per water,<br>per mask layer                  | Masks,<br>Celma tape,<br>PG tape                           |  |

| American Microsystems, Inc.<br>3800 Homestead Roed<br>Santa Clars. CA 95051<br>(408) 246-0330<br>Jeny Crosby<br>Product Manager,<br>COT Products |                                   | J.Sym<br>(nMOS I)<br>Sym<br>(nMOS II)<br>Sym,<br>Gym | 7.5µm              |                                                | <i>ј</i><br>7.5µm                            | /<br>5µm<br>(CMOS I),<br>3µm<br>(CMOS II)<br>single<br>or<br>double<br>metal  |                                           | ų                      | Working plate<br>plate input:<br>\$75,000 yr.<br>PG or Calma<br>ir.put: 10<br>times angi-<br>teering cost<br>for first year | Development<br>cost:<br>\$14,000 to<br>\$30,000                                                                                    | Caima tape,<br>PG tape,<br>working plates                  |  |

| ASEA HAFO 66 Bovet Road Sari Mateo, CA 94402 (415) 574-5400 Anders Dejenfelt, Sales Manager                                                      |                                   | •                                                    | •                  |                                                | J<br>Syste<br>(Byste)                        | /<br>2µm<br>(10;:m)<br>CMOS:<br>SOS                                           | ·                                         | *                      | One batch<br>(40 me-pate<br>CMOS waters<br>or 20 CMOS/<br>SOS waters)                                                       | \$20,000 (incl.<br>mask and water-<br>tab charges)                                                                                 | Masks,<br>PG tape,<br>CIF (PG tape<br>or CIF<br>preferred) |  |

| Cherry Semiconductor Corp.<br>2000 S. County Trail<br>E. Greenwich, RI 02818<br>(401) 885-3600<br>David Pryce<br>Marketing Manager               |                                   | -                                                    |                    |                                                |                                              |                                                                               | finear,<br>ffL,<br>eptoelect.             | r                      | 1/10 waters/<br>snorth                                                                                                      | \$3000 per<br>engineering run<br>(10 waters)<br>Prod cost:<br>\$120 to \$160<br>per water<br>(1,000 to 5,000<br>waters/mo.)        | Applican tape,<br>Calma tape,<br>masks,<br>scaled drawings |  |

| Citel<br>3050 Raymond Street<br>Senta Clara. CA 95050<br>(408) 727-6562<br>Gary Hess<br>Marketing Director                                       | ار<br>5µm<br>(10µm)               | /<br>3µm<br>(8µm)<br>4µm<br>(8µm)<br>5µm<br>(10µm)   | /<br>5µm<br>(10µm) | ر<br>5 <sub>p.</sub> m<br>(10 <sub>p.</sub> m) | /<br>5µm<br>(10µm)                           | -/<br>3µm<br>(Ցµm)<br>4µm<br>(Ցµm)<br>5µm<br>(10µm)<br>5µm<br>2-łayer<br>poly | Linear<br>6μm,<br>f <sup>2</sup> L<br>Sμm | 3° and 4°              | Lot: 25<br>water starts                                                                                                     | Variable                                                                                                                           | Calma tape,<br>masks,<br>PG tape                           |  |

| Comdial Semiconductor Serv.<br>1230 Bordeaux Drive<br>Sunnyvale, CA 94086<br>(408) 744-1800<br>Gery Kennedy<br>VP and General Manager            |                                   | /<br>Յրտ<br>(Ցրտ),<br>4րտ<br>(Ձրտ)                   |                    |                                                |                                              | / dum (Bum), dum (Bum), 2-layer poly, Sum (Bum)                               |                                           | t.                     | 25 walers<br>(Comdul<br>apocalizes<br>in quick-<br>tumeround<br>prototyping)                                                | \$7000 to \$8000 for Jum HMOS (10 or 15 duys) \$7000 to \$7000 for 4µm CMOS (10 or 15 days) Consult factory for other requirements | Calma tape,<br>CIF,<br>masks,<br>e-beam tape               |  |

| Exar Integrated Systems, Inc.<br>750 Patoniar Avenue<br>Europycale, CA 94088<br>(460) 732-7970<br>Tiruston Awall                                 |                                   | J<br>Syam                                            |                    |                                                | Sport.                                       | Sp.m                                                                          | j<br>Linear, .<br>PL                      | *                      | 250<br>waterstyr.                                                                                                           | Consult factory                                                                                                                    | Celma tapo,<br>masks<br>(pveterned)                        |  |

| Post White-<br>Processing<br>Services<br>(water<br>probing<br>packaging,<br>testing, etc.) | Normal<br>Tumeround Time                                                                                                                    | Water<br>Acceptable<br>Critens<br>(std. proces*<br>control mo stor)                                           | Technical<br>Interaction<br>Between Foundry<br>and Customer                       | Availability of<br>Design Rules<br>for Venous<br>Processes | Must<br>Customer<br>Sign Non-<br>disclosure<br>Agreements | Simulator<br>Parameters<br>Available                                   | Second-<br>Source<br>Agreements                                                 | WR<br>Foundry<br>Modify<br>Process? | Processes<br>Available Within<br>Next & Months                                                                                             |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| (none)                                                                                     | Masks to waters:<br>6 wis.<br>PG tape to waters;<br>10 wis.                                                                                 | Test monitors<br>supplied by<br>Acrush or by<br>customer                                                      | Intel engi-<br>neering raview;<br>updates as<br>required                          | A                                                          | Ves                                                       | Pricess emu-<br>lation support<br>via PRODEM<br>(similar to<br>SUPREM) | (none)                                                                          | Ves                                 | Rad hard me-<br>gate CMOS<br>June 1963<br>Sigate CMOS<br>(Spm): Nov. 1963                                                                  |

| Probing.<br>packaging.<br>packaged-<br>part testing                                        | PG tape to cut-and-<br>go's 4 to 5 wis<br>Database tape to<br>cut-and-go's:<br>5 to 6 wis.<br>PG tape to<br>packaged parts:<br>7 to 10 wis. | AMI process<br>control montor<br>on all waters;<br>will add<br>customer PCM<br>ill requested                  | Formal review<br>etter each<br>phase of AMI<br>development<br>cycle<br>(optional) | Avartable<br>for all<br>processes                          | Yes                                                       | ASPEC                                                                  | In negobation<br>with several<br>companies                                      | Yes<br>(V;<br>and<br>implants)      | nMOS III (2µm):<br>3083<br>CMOS I (shrink<br>to 4µm) 3023<br>CMOS II (10V):<br>2083<br>CMOS III (2µm):<br>1084<br>EEPPROM process:<br>4084 |

| Probing,<br>packaging,<br>packaged-<br>part testing,<br>burn-in                            | PG tape to wafers:<br>6 wis (CMOS)<br>7 wis. (CMOS:SOS)<br>Add 3 wis for<br>packaging testing                                               | ASEA HAFO-<br>supplied<br>process-<br>param modules<br>(PPMs) and<br>yiuld-<br>measurement<br>modules (VMM's) | Initial review                                                                    | All processes<br>provided                                  | Ves .                                                     | SPICE 2G4<br>and<br>SPICE 2G5                                          | Process is<br>RCA-<br>companble                                                 | Yes,<br>(large<br>order)            | 4-inch process<br>time with dry<br>processing and<br>positive photo-<br>resist 4Q83                                                        |

| Probing, packaging, testing                                                                | 8 wks. (typical) Design rule cher'., 1 wk.; Mask generation, 2 wks.; Fabrication, 5 wks.                                                    | Chemy-<br>supplied PCM                                                                                        | Design reviews<br>to establish<br>crount<br>process<br>requirements               | AJ                                                         | Maybe                                                     | ISPICE<br>(NCSS)                                                       | Yes<br>(not<br>specified)                                                       | Yes                                 | (none<br>contemplated)                                                                                                                     |

| Probing,<br>packaging,<br>packaged-<br>part testing                                        | Masks to packaged parts (production parts, hybrai) nMOS pMOS 6-8 wks CMOS, 7-9 wks.                                                         | Citet- or<br>customer-<br>supplied test<br>circuit                                                            | Intal review                                                                      | A.I                                                        | Ves                                                       | Electrical<br>(not simulator)<br>parameters<br>supplied                | (not<br>specified)                                                              | Depends<br>on<br>individual<br>case | 4" bipolar<br>capability.<br>Dec 31, 1983                                                                                                  |

| Probing,<br>packaging,<br>packaged-<br>part tosting                                        | Masks to waters<br>(prototype):<br>5 wkg days (HMOS)<br>10 wkg days (CMOS)<br>Masks to tested<br>waters (Ory: 500):<br>15 wkg days          | Comdust- o-<br>customer-<br>supplied test<br>device                                                           | Frital review                                                                     | AS                                                         | No 、                                                      | SPICE                                                                  | Unofficially, process is compatible with several large semi-conductor suppliers | Open for discussion                 | 3-µm p-we?<br>CMOS (6-m metal<br>proh): 4053<br>3-µm n-we!!<br>CMOS process:<br>4083                                                       |

| Probing,<br>packaging,<br>packagod-<br>part testing                                        | Masks to waters out:<br>4 to 6 wis.<br>Add 2 to 4 wis. for<br>tested devices                                                                | Example or customer-<br>supplied PCM (in-house PCM preferred)                                                 | Initial review<br>plus any<br>required<br>process<br>metrices                     | AI                                                         | Yes                                                       | (not<br>svalable)                                                      | Rohm<br>(parent<br>company<br>in Japan)                                         | Yes<br>(negotable)                  | (not specified)                                                                                                                            |

|                                                                                                                                                                  |                    |                                         |                                 | num Feetu          | res Aveleb<br>e S-ze Get<br>h shown in |                                          | )                                                          |                                 | Mountum<br>Production                                          | Cost Per                                                                                             | Design Format<br>trom Customer                          |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------|---------------------------------|--------------------|----------------------------------------|------------------------------------------|------------------------------------------------------------|---------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|

| Company<br>Contact Person                                                                                                                                        | M-G                | MOS<br>8-G                              | Me-G                            | vos<br>s-G         | Me-G                                   | MOS<br>8-G                               | Bipoler                                                    | Prod<br>Weler<br>Size           | Procurements<br>(5 or weters<br>per year)                      | Prototype Run<br>(with prod cost<br>if available)                                                    |                                                         |  |

| Four-Phase Systems, Inc.<br>10700 N De Anza Bird<br>Cupertino, CA 95014<br>(408) 255-0900<br>Larry Regle<br>Marketing Manager                                    | j<br>7µm           | . ј<br>Sµm                              | S <sub>p</sub> .m               |                    | ./<br>7µт                              | J<br>Species                             |                                                            | *                               | (not<br>defi. ad)                                              | Typical<br>engineering<br>qualification<br>run: 85,000                                               | Working plates,<br>PG or data-<br>base tape             |  |

| General Instrument Microelectronics Division 600 W. John St., C.S. 620 Hicksville, NY 11802 (516) 733-3611  J.E. Edwards                                         |                    | dens<br>(Syum)                          |                                 |                    |                                        | /<br>5pm<br>(10pm)                       | -                                                          | •                               | 50 waters                                                      | Prototype run<br>(including mask<br>costs): \$8000<br>(50 tested<br>protritypes or<br>\$ wafers out) | Cama GDSII tape<br>(preferred).<br>PG tape.<br>masks    |  |

| GTE Microcircuits<br>2000 W. 14th Street<br>Tempe, AZ 85281<br>(602) 968-4431<br>Fred M. McWittams<br>Sales Managur,<br>Salcon Foundry                           |                    | J<br>Span                               |                                 | ,                  |                                        | 4µm,<br>ISO <sup>2</sup><br>CMOS,<br>4µm | J<br>Linear                                                | ٣                               | 100<br>welers/yr.<br>(engineering<br>qual. runs:<br>25 welers) | Consult fectory                                                                                      | Calma tape,<br>masks,<br>PG tape                        |  |

| Flarris Semiconductor<br>P:O. Box 863<br>Melbourne, Ft. 32901<br>(305) 729-5681<br>Dennis Gaetano<br>Mgr., Mkg. Planning                                         | /<br>Sµm<br>(15µm) |                                         | J<br>Spm<br>(1Spm)              | /<br>4µm<br>(10µm) |                                        | /<br>Зµт<br>(Вµт)                        | /<br>STL,<br>2-layer<br>metal,<br>14µm<br>metal<br>pitch   | 4°<br>MOS;<br>3°<br>b-<br>poler | \$100,000 ye.                                                  | Consult factory                                                                                      | PG tape or<br>Calma tape<br>(preferred);<br>masks       |  |

| Hughes Aircraft Co.<br>Solid State Products Div<br>500 Supenor Avenue<br>Newport Beach, CA 92663<br>(714) 759-2964<br>P. Jennifer Huffer<br>Div. Advart. Manager |                    |                                         |                                 |                    | j<br>djem                              | /<br>3µm                                 |                                                            | 3"<br>and<br>4"                 | 25-water<br>bits                                               | Consult fectory                                                                                      | Calma tape,<br>PG tape                                  |  |

| Intel Corp.<br>5000 W. Wiltams Field Road<br>Chandler, AZ 85224<br>(602) 961-8051<br>Bob Koehler                                                                 | ·                  | /<br>HMOSI<br>3.5µm*,<br>HMOSII<br>2µm* |                                 |                    |                                        | /<br>2µm°<br>CHMO6                       |                                                            | 4" and 6"                       | 10,000<br>unts-yr.<br>("classical<br>foundry")                 | Consult factory                                                                                      | Applicon tape,<br>Calma tape                            |  |

| Marketing Manager  International Microelectronic Products 2830 N First Street San Jose, CA 95134 (408) 262-9100  Bob Gerdner Marketing Manager                   |                    | /<br>3µm<br>(8µm),<br>4µm,<br>5µm       |                                 |                    |                                        | /<br>Зыт<br>(Выт),<br>4ыт,<br>8ыт        | •                                                          | ď                               | \$50,000 yr.                                                   | Prod cost<br>(Sµm CMOS):<br>\$6500 to \$6500<br>plus mask costs                                      | Celma tape or<br>Applicon tape<br>(preferred),<br>masks |  |

| Marketing Manager  Micrel 1235 Midas Way Surnyvale, CA 94086 (408) 245-2500  Stan Ericason Director, Sales-18ktg                                                 |                    | /<br>4µт<br>(10µт)                      | /<br>4µm<br>(10 <sub>µ</sub> m) | /<br>4µm<br>(10µm) | ,*<br>4µm<br>(10µm)                    | /<br>4µm<br>(10µm)                       | /<br>Linear<br>TTL                                         | r                               | 25 water<br>starts                                             | Engineering run,<br>(25 water<br>starts): \$2500                                                     | Database tape,<br>masks,<br>PG tape                     |  |

| Micro-Circuit Engineering, Inc.<br>1111 Farfield (Inve<br>W Palm Bouch, FL 33407<br>(306) 845-2837<br>Drk Schwebe<br>Marketing Manager                           |                    |                                         |                                 |                    | ј<br>Бјит<br>(10 <sub>ји</sub> т)      | /<br>Տատ<br>(10ատ)                       | bifet<br>and<br>biMOS<br>processes;<br>20V,<br>40V,<br>80V | e e                             | Order<br>sommoment,<br>\$100,000                               | (consult factory)                                                                                    | Celme tape,<br>Cif,<br>masks,<br>PG tape                |  |

<sup>, &</sup>quot;Intel M645 "effective channel length" which may be a lower number than the aquivalent "drain channel length" apecified by other vendors

|                                                                                                 |                                                                                                              | •                                                                                                |                                                                                                                                     |                                                               |                                                           |                                                           |                                                                         |                                                      |                                                                                                                                         |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Processed                                                                                       |                                                                                                              |                                                                                                  |                                                                                                                                     |                                                               |                                                           |                                                           |                                                                         |                                                      |                                                                                                                                         |

| (water<br>protong,<br>packaging,<br>terting, etc.)                                              | Normal<br>Sumeround Time                                                                                     | Weler<br>Acceptable<br>Criteria<br>(sid process<br>control monitor)                              | Technical<br>Interaction<br>Between Foundry<br>and Customer                                                                         | Availability of<br>Design Rules<br>for Vanous<br>Processes    | Must<br>Custome:<br>Sign Non-<br>disclosure<br>Agreements | Simulator<br>Parameters<br>Avertable                      | Second-<br>Source<br>Agreements                                         | Wa<br>Foundry<br>Modity<br>Process?                  | Processes<br>Available Within<br>Next & Munitis                                                                                         |

| Probing:<br>packaging:<br>packaged-<br>pari testing<br>burn-tr                                  | Masks to waters: 4 whs (typical) Add 1 wh for 6.35embly/test of amed tots                                    | Four-Phase or<br>customer-<br>supplied PCM<br>Wit also work<br>on a good<br>de-permater<br>backs | "Constant"<br>Interaction                                                                                                           | All                                                           | No .                                                      | Available<br>(not specified)<br>but "serely<br>requested" | (no formal<br>egreenients)                                              | Yes                                                  | Some 4"water production by 4083 Plans to increase volume in 4 µm Sigate CMOS process by 3083                                            |

| Probing,<br>packaging,<br>packaged-<br>part<br>testing                                          | Calma tape to waters:<br>8-10 weeks (typical)<br>Add 2-3 weeks for<br>packaged devices                       | Electrical<br>parameters<br>measured on<br>GI 'est<br>eleuctures                                 | Initial review,<br>tohow-up<br>reviews as<br>required                                                                               | All (3 <sub>µm</sub> process specs not finel as of 4/25/83)   | Yes .                                                     | (not available)                                           | (no formal<br>agreements)                                               | Yes<br>(within<br>firmts)                            | 3µm Signate<br>nMOS process<br>avait 4083<br>3µm Signate<br>CMOS process<br>avait 4083                                                  |

| Probing,<br>packaging                                                                           | Masks to waters:<br>5-6 weeks (typical)                                                                      | GTE-supplied<br>PCM                                                                              | Periodic<br>process and<br>design reviews                                                                                           | AB                                                            | Ves                                                       | SPICE.<br>TEGAS                                           | Made                                                                    | Maybe<br>(depends<br>on size of<br>order)            | 3 <sub>m</sub> m, 2-layer<br>metal 5-pate<br>CMGS avail.<br>SQ83                                                                        |

| Probing,<br>packaging,<br>packaged-<br>part<br>lesting,<br>burn-in                              | Calma tape to probed waters: 10-12 weeks (typical) Add 6-12 weeks for packaged, tested parts                 | (negotable)                                                                                      | Depends on<br>customer<br>requirements                                                                                              | Al                                                            | Yes .                                                     | SLICE<br>(Harris'<br>version of<br>SPICE)                 | (Rone)                                                                  | Ves<br>of it<br>makes<br>"business<br>sense")        | 2µm, 2-layer<br>metal CMOS,<br>under develop-<br>ment for gate<br>arrays, should<br>be avail, as<br>foundly process<br>by end of 1983   |

| Probing<br>packaging,<br>packaged-<br>part<br>testing                                           | PG tupe to mests:<br>,10 days<br>Mastis to finished<br>waters: 25 days                                       | Standard<br>Huges PCM                                                                            | Pariodic<br>process and<br>design reviews                                                                                           | 43                                                            | Ves                                                       | SPICE<br>(worst-case<br>process<br>modules)               | Yes (not<br>apacified)                                                  | Vas<br>(il volume<br>warrants il)                    | (nat specified)                                                                                                                         |

| Protting,<br>packaged,<br>parkaged-<br>part<br>sisting,<br>character-<br>ization<br>(skew runs) | Database tape to tested waters (prototype run): 9-12 weeks                                                   | Intel PCM<br>ahrays stepped<br>into water                                                        | Intel prefers<br>to work with<br>outstomers who<br>design chips<br>chips using<br>the ICEL <sup>4</sup><br>standard cell<br>program | All                                                           | Ves                                                       | ASPEC<br>(usually reqs.<br>non-disclosure<br>agreement)   | No                                                                      | No                                                   | (not specified)                                                                                                                         |

| Probing,<br>packaging,<br>packaged-<br>part<br>testing,<br>burn-in                              | Database tape to packaged lested parts: 6 weeks (5µm) 7 weeks (3µm CMOS) (3 weeks cycle avail at added cost) | BMP PCM<br>(preferred) or<br>customer-<br>supplied PCM                                           | Inital review<br>plus any<br>necessary<br>tollow-up                                                                                 | Al                                                            | Yes                                                       | Available<br>(not specified)                              | Comdial<br>(others in<br>negotiation)                                   | Yes<br>(usually<br>for eng<br>prototype<br>sun only) | 2-layer poly<br>and 15V CMOS<br>processes by<br>4063 2-layer<br>metal by 4083                                                           |

| Probing,<br>packaging,<br>packagod-<br>pert<br>tosting,<br>burn-er                              | PG tape to waters<br>5-7 weeks (typical)<br>Add 3-4 weeks for<br>peckaged, tosted<br>devices                 | Morel- or<br>customer-<br>supplies PCM                                                           | Initial review,<br>tohowup<br>reviews as<br>required                                                                                | All<br>(design rules<br>generally<br>supplied by<br>oustomer) | No (Micrel will sign non-drict for cust supplied nives)   | (not available)                                           | Will modify<br>process to be<br>mask compatible<br>with prime<br>source | Yos<br>(see left)                                    | 4" waters by<br>4083 Schonky<br>TTL (3-u ep.)<br>by 4083                                                                                |

| Probing,<br>packaging,<br>packaged-<br>part<br>testing                                          | Calms tipe to —-<br>packaged tested<br>samplus: 7-11 weeks                                                   | MCE-supplied<br>PCM                                                                              | Penadic<br>processidesign<br>neviews                                                                                                | AI .                                                          | Ves                                                       | SPICE.<br>ASPEC-G2                                        | Yes<br>Linear<br>Technology<br>Corp.                                    | Ves                                                  | 3µm oxide<br>solate J Si-gate<br>CMOS by 12 83<br>20V detective<br>split types<br>by 12 R3 40V<br>detective<br>stol bipular<br>by 12 83 |

|                                                                                                                                                         |          |                                              |            | mum Featu  | pes Aveleti<br>re Size Get<br>h ehown en |                                                                        | .)                                                                            |                             | Minimum<br>Production                                                                                                 | Cost Par                                                                                                            | Design Format<br>from Customer                                    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------|------------|------------|------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|

| Company<br>Contact Parson                                                                                                                               | M+G      | MOS<br>S-G                                   | Mo-G       | Mos<br>6-G | Me-G                                     | MO.<br>S-G                                                             | Byoter                                                                        | Prod.<br>Water<br>Size      | Paquirements<br>(5 or waters<br>per year)                                                                             | Prototype Run<br>(with prod cost,<br>if everlable)                                                                  |                                                                   |  |

| Mitel Semiconductor<br>360 Legyet Drive<br>P.O. Box 13320<br>Kanata, Ortano KZK 1XS<br>Canada<br>(613) 532-5630<br>Gene Cohen<br>Custom Prod. Line Mgr. |          |                                              |            |            | ,                                        | ~ 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5                                |                                                                               | 4                           | Water run:<br>20 waters<br>Order:<br>\$10,000                                                                         | (sec left)                                                                                                          | Canta laps,<br>PG laps,<br>masks                                  |  |

| Mosfet-Micro Labs, Inc.<br>Pern Centre Plaza<br>Ouekartown, PA 18951<br>(215) 536-2104<br>Robert O. Campbell<br>Marketing Manager                       | Эмля     | /<br>3µ/h<br>(also<br>tung-<br>sten<br>gete) | /<br>Syrn  | J<br>Sym   | ý<br>Spm                                 | /<br>3µm<br>(siso<br>amp-<br>son<br>gate)                              | -                                                                             | 3"                          | Prod. cost:<br>\$2000 (me-<br>gate pMOS,<br>nMOS) to<br>\$3500 (Si-<br>gate CMOS)                                     | (nee left)                                                                                                          | PG Inpe,<br>masks                                                 |  |

| National Semiconductor<br>2900 Semiconductor Drive<br>Sarta Clara, CA 95051<br>(400) 737-6055<br>Richard Y. Barck<br>Dir. MOSALSI Midg.                 | J<br>Sum | /<br>Sure,<br>dum to<br>Sure                 | g<br>Bysta |            | /<br>Туыт                                | Julia<br>Single<br>and<br>dual<br>poly,<br>Syun<br>dual<br>metal       | PL, SV<br>Schottky;<br>5-100V non-<br>Schottky;<br>SV gatd-daps               | € and<br>5°                 | Business per<br>family:<br>\$159,000 to<br>\$200,000 yr.<br>(Not inter-<br>asted in<br>prototype<br>business<br>only) | Prototype lot<br>charge (not<br>incl masi/lest<br>charges):<br>\$225-water<br>(me-gate)<br>\$350-water<br>(Si-gate) | Celms tape<br>(preferred):<br>Applican tape,<br>masks,<br>PG tape |  |

| NCR Corporation Microelectronics Div. 2001 Denfield Court Ft. Colons, CO 80525 (303) 226-9580 Dave Nowman Prod. Strategy Mgr.                           |          | J<br>Syste<br>Simple<br>or<br>dust<br>motal  |            |            |                                          | /<br>3µ/n<br>(7.5µ/n)<br>single<br>or<br>dual<br>metal                 |                                                                               |                             | 500 wafers<br>for non-sid.<br>processing;<br>100 wafers<br>otherwise                                                  | (consult factory)                                                                                                   | Calma tape<br>(preferred);<br>PG tape,<br>masks                   |  |

| Nitron<br>10420 Bubb Road<br>Cuperino, CA 95014<br>(408) 255-7550<br>Robert Miller<br>VP, Mildg. and Sales                                              |          |                                              |            |            | /<br>Տրտ<br>(12µm)                       | /<br>4μπ<br>(12μπ)                                                     |                                                                               | 3"<br>and<br>4"             | \$100,000 yr.<br>(including<br>sign-recur-<br>sing costs)                                                             | (consult factory)                                                                                                   | Calma tape,<br>PG tape,<br>masks,<br>rendes                       |  |

| Plessey 1641 Kacor Avenue Irvine, CA 92714 (714) 540-9937 Peter Minett Product Midg Mgr                                                                 |          | /<br>5µm<br>(10µm),<br>6µm<br>(12µm)         |            |            |                                          | /<br>2.5 <sub>7</sub> ,m<br>(Вµт),<br>4µт<br>(9 6µm),<br>5µт<br>(12µm) | J<br>3µm ECL,<br>4µm ECL                                                      | 3"<br>and ,<br>4"           | \$50,000 yr. ·                                                                                                        | (consult factory)                                                                                                   | Calma tape,<br>mesks,<br>PG tape                                  |  |

| Polycore Electronics, Inc.<br>1107 Tournahne Drive<br>Newbury Part. CA 91320<br>(805) 498-8832<br>S.K. Leong<br>Vice President                          |          |                                              |            |            | /<br>7µm<br>(>20V<br>process<br>evail)   |                                                                        | /<br>Linear,<br>Pi-<br>defectno<br>isolation<br>combination<br>CMOS:<br>Brear | r                           | 24 water<br>engineering<br>lot                                                                                        | Engineering - nurs: \$3020 to \$6000 Production costs (avg.): \$100 water (CMOS) \$130 water (finear)               | Worlung plates                                                    |  |

| RCA<br>Solid State Drv.<br>Rt. 202<br>Somerville, NJ 08875<br>(201) 665-6000<br>Jurgen W. Schwer<br>Mintg. Myr., Custom Products                        |          |                                              |            |            | ј<br>7 <sub>р</sub> л                    | /<br>Зµт, -<br>Бµт<br>СМОБ/<br>ВОВ.<br>Зµт,<br>4µт,                    |                                                                               | 4"<br>CJ'<br>SUMOS/<br>SOS) | (consult factory)<br>(RICA offers<br>toundry<br>services on<br>selected<br>basis only)                                | Evaluation-<br>tot costs<br>\$20,000-\$30,099<br>Tooling costs<br>\$10,000-\$20,000                                 | Celma tape                                                        |  |

| Semi Processes, Inc.<br>1971 N. Capital Ave.<br>Sen Ave., CA 95/132<br>(408) 945-1500<br>C.B. Detrick<br>Waler Service Mgr.                             |          |                                              |            |            | 4.Spm                                    | J<br>4.Sµm                                                             |                                                                               | r                           | (not<br>apacified)                                                                                                    | Typical cost for evaluation num (CMOS megate): \$2500                                                               | Masks                                                             |  |

| Pos' Wa'er                                                                           |                                                                                                                    |                                                                    |                                                                       |                                                            |                                                           |                                      |                                                         |                                      |                                                                                                                             |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Pricessing<br>Services<br>(we'er<br>pricing<br>puckeying,<br>escript etc.)           | Normal -<br>Turnaround Time                                                                                        | Water<br>Acceptable<br>Critena<br>(std process<br>control monitor) | Technical<br>Interaction<br>Between Foundry<br>and Customer           | Availability of<br>Design Rules<br>for Vanous<br>Processes | Must<br>Customer<br>Sign Non-<br>disclosure<br>Agreements | Simulator<br>Parameters<br>Available | Second-<br>Source<br>Agreements                         | Wile<br>Foundry<br>Mosky<br>Process? | Processes<br>Available Witten<br>Next 6 Monets                                                                              |

| Probing.<br>packaging<br>packaged-<br>part<br>secting                                | trasks to waters:<br>6 weeks (typical)<br>Add 4 weeks from<br>PG tape, add<br>2 weeks to packaged<br>parts         | Metal PCM                                                          | Technical<br>general<br>meetings<br>gossible                          | AZ .                                                       | Ves                                                       | SPICE                                | GTE<br>Microonulis                                      | Yes<br>(negotable)                   | (not specified)                                                                                                             |

| (services<br>evaliable<br>locally<br>elsewhere)                                      | Masks to test<br>prouts 3 to<br>4 weeks                                                                            | (Nexòle)                                                           | Interaction<br>with MML's<br>engineers/<br>technicians<br>as required | Selfs layout<br>rules for<br>\$250                         | _                                                         | (not available)                      | (sometimes)                                             | Yes                                  | High-votage<br>MOS, also<br>working wifi<br>V-groove LIOS                                                                   |

| Probing.<br>packaging.<br>packaged-<br>part<br>testing.<br>reliability<br>processing | Database tape to PCM-tosted waters: 6 to 10 weeks (depending on process) For packaged parts, add 4 to 6 weeks      | Standard<br>National PCM                                           | Instal and<br>follow-up<br>process/design<br>reviews as<br>required   | AS                                                         | Ves                                                       | SNAP<br>(NSC internal)               | Yes<br>(not specified)                                  | Yes<br>(mnor)                        | 2µm double-<br>metal n-well<br>CMOS; mid 84                                                                                 |

| Probing.<br>packaging,<br>packaged-<br>part<br>assing,<br>burn-in                    | Calma tope to tested waters: 6 weeks (typical)                                                                     | Prefers to<br>step-in<br>NCR PCM                                   | evital review<br>Followup<br>structure as<br>necessary                | Negotable                                                  |                                                           | SPICE                                | Not yet<br>(in negotation<br>with 3 large<br>companies) | Yes<br>(depends<br>on<br>volume)     | Will be able to manufacture devices (with poly-to-substrate capactors) for analog functions in CMOS circuits by end of 1953 |

| Probing,<br>packaging,<br>packaged-<br>part<br>tosting,<br>butti-in                  | Masks to tested waters 4 to 6 weeks From PC tape add 2 weeks, to peckaged lested parts; add 4 weeks                | Nitron PCM<br>(preferred) or<br>customen<br>supplied PCM           | Initial and<br>follow-up<br>process/design<br>reviews                 | For older processes                                        | Yas                                                       | (not available)                      | Universal<br>Semiconductor<br>(Si-gate)                 | Yes<br>(within<br>hmits)             | 3µm S-gate<br>CMOS available<br>by 1084                                                                                     |

| Probing,<br>packaging,<br>packaged-<br>part<br>testing                               | Masks to waters:<br>2 wks<br>PG tape to tested<br>devices: 6 wks                                                   | Plessey PCM                                                        | Inital review                                                         | A                                                          | Yes                                                       | SPICE                                | Yes<br>(not specified)                                  | No                                   | 2.5-µm CMOS<br>by end of 1983                                                                                               |

| Probing,<br>(packaging<br>in far East<br>and testing<br>can be<br>arranged)          | Fast-turnaround engineering runs, masks to waters 2 wis (CMOS) 3 wits (knear) Add 2 to 3 days for sample packaging | Polycore-<br>supplied PCM                                          | Intial review                                                         | AI                                                         | No                                                        | (not available)                      | (no formal - agreements)                                | (es                                  | (not disclosed)                                                                                                             |

| Probing,<br>packaging,<br>packagod-<br>pari<br>testrig,<br>burn-in                   | (not specified)                                                                                                    | RCAs Water<br>Acceptance<br>Test (WAT)<br>onlenge                  | Instal formal<br>design reviews<br>(required)                         | AJ                                                         | · Yes                                                     | R-CAP                                | (no formal<br>agreements)                               | No                                   | (none)                                                                                                                      |

| Basic<br>testing                                                                     | Masks to waters: 4<br>wks. (me gate CMOS)<br>6 to 8 wks.<br>(Si-gate CMOS)                                         | Mulually<br>agreed-upon<br>PCM                                     | Penodic<br>interestion                                                | AI .                                                       | For Si-<br>gate CMOS<br>process<br>enly                   |                                      | (not specified)                                         | Yes                                  | 5" water<br>production by<br>end of 1983                                                                                    |

|                                                                                                                                             |     |                                                                                                  |      | num Feet.                                   | pes Avaitable<br>se Size Gere<br>habown in j |                                                                                      | .)                                                            | -                     | Minimum<br>Production                                                                                                               | Cost Per                                                                                                                                     |                                                                               |  |