# OCCASION

This publication has been made available to the public on the occasion of the 50<sup>th</sup> anniversary of the United Nations Industrial Development Organisation.

TOGETHER

for a sustainable future

## DISCLAIMER

This document has been produced without formal United Nations editing. The designations employed and the presentation of the material in this document do not imply the expression of any opinion whatsoever on the part of the Secretariat of the United Nations Industrial Development Organization (UNIDO) concerning the legal status of any country, territory, city or area or of its authorities, or concerning the delimitation of its frontiers or boundaries, or its economic system or degree of development. Designations such as "developed", "industrialized" and "developing" are intended for statistical convenience and do not necessarily express a judgment about the stage reached by a particular country or area in the development process. Mention of firm names or commercial products does not constitute an endorsement by UNIDO.

# FAIR USE POLICY

Any part of this publication may be quoted and referenced for educational and research purposes without additional permission from UNIDO. However, those who make use of quoting and referencing this publication are requested to follow the Fair Use Policy of giving due credit to UNIDO.

# CONTACT

Please contact <u>publications@unido.org</u> for further information concerning UNIDO publications.

For more information about UNIDO, please visit us at <u>www.unido.org</u>

RESTRICTED

DP/ID/SER.B/641 16 February 1989 ORIGINAL: ENGLISH

Ι,

## SEMICONDUCTOR DEVICES AND ELECTRCNIC SUB-SYSTEMS FOR TRANSPORTATION

DP/IND/84/015

INDIA

Terminal report\*

Prepared for the Government of India by the United Nations Industrial Development Organization, acting as executing agency for the United Nations Development Programme

### Based on the work of the Central Electronics Engineering Research Enstitute prepared by the National Project Director

Backstopping officer: J. Pürkus Engineering Industries Branch

United Nations Industrial Development Organization

Vienna

\* This document has not been edited.

V.89 51648

1

# CONTENTS

| <u>S.No.</u>  | Description                                                                 | Pages |

|---------------|-----------------------------------------------------------------------------|-------|

| I             | INTRODUCTION                                                                | 3     |

| 11            | OBJECTIVES                                                                  | 4     |

| III           | ACTIVITIES CARRIED OUT &<br>OUTPUTS ACHIEVED                                | 6     |

| IV            | ACHIEVEMENTS OF OBJECTIVES                                                  | 75    |

| v             | UTILIZATION OF PROJECT RESULTS                                              | 76    |

| VI            | FINDINGS                                                                    | 77    |

| VII           | RECOMMENDATIONS                                                             | 80    |

| ANNEXURE-I    | CONSTITUTION OF PROJECT<br>ADVISORY COMMITTEE AND ITS<br>TERMS OF REFERENCE | 82    |

| ANNEXURE-11   | UNDP PROVIDED EXPERTS/CONSULTANTS                                           | 84    |

| ANNEXURE-III  | NATIONAL PERSONNEL                                                          | 86    |

| ANNEXURE-IV   | FELLOWSHIP TRAINING                                                         | 90    |

| ANNEXURE-V    | STUDY TOURS                                                                 | 92    |

| ANNEXURE-VI   | EQUIPMENT PROCURED UNDER<br>UNDP FUNDS                                      | 93    |

| ANNEXURE-VII  | EQUIPMENT PROCURED UNDER<br>COUNTER PART FUNDS                              | 94    |

| ANNEXURE-VIII | NOTE ON THE NATURE OF THE<br>PRODUCTS AND PROCESSES                         | 96    |

| ANNEXNURE-IX  | HARD AND SOFT OUTPUTS                                                       | 100   |

| ANNEXURE -X   | LIST OF ENGINEERS/SCIENTISTS<br>TRAINED FROM WITHIN THE COUNTRY             | 116   |

.

|                 | INKAGES ESTABLISHED WITH IN<br>RGANIZATIONS                | DUSTRIAL 123 |

|-----------------|------------------------------------------------------------|--------------|

| ANNEXURE -XII C | OLLABORATIVE RESEARCH PROGR                                | MME 130      |

| ANNEXURE -XIII  | LIST OF SEMINARS/SYMPOSIA/W                                | ORKSHOPS 133 |

|                 | ACTION TAKEN BY CEERI ON TH<br>RECOMMENDATIONS OF UNDP CON |              |

|                 | ACTION TAKEN ON THE MAIN<br>RECOMMENDATIONS OF THE PAC     | 146          |

٠

٠

•

.

.

#### 1. INTRODUCTION:

- 1. This terminal repor briefly presents an analysis of the project implementation and results obtained up to Nov. 20, 1988. It describes the activities, outputs and the extent to which the project objectives could be achieved and in line with the project document, it concludes with the recommendations for future UNDP assistance to translate the results achieved and likely to be achieved in the near future due to the expertise facilities developed by the project, into prototype fabrication and technology utilisation.

- 2. UNITED NATIONS INDUSTRIAL DEVELOPMENT ORGANIZATION (UNIDO) was the executing agency and COUNCIL OF SCIENTIFIC AND INDUSTRIAL RESEARCH (CSIR) India through Central Electronics Engineering Research Institute (CEERI) Pilani (Rajasthan) India was the implementing agency for the project.

- 3. The project commenced in Nov, 1984 four months behind Schedule of estimated starting date i.e. July, 1984. The project duration of three years was extended by one year up to Oct. 1988 on the basis of careful scrutiny of availability of materials & equipment and recommendation of Tripartite Review meeting held in January, 1987. The international component of the planned input of USS 1,467,000 was reduced to US\$ 1,402,335 (budget revision F). It was revised upwards to US\$ 1,682,335 (budget revision J) on the recommendations of TPR meeting of Jan, 1987 and covers a total allotment of US\$ 1,687,395 under budget revision L. The counterpart contribution planned was Rs.13,900,000 and against this the contribution of Rs.23,600,000 (Rs.18,800,000 for equipment Rs.4,800,000 for consumables) has been utilised. The actual counterpart inputs are estimated to be higher.

**OBJECTIVES**

- 5. Basically Electronic systems needed for all the Transportation systems are of three types: electronic control systems, data handling systems and safety systems. In view of the inherent advantages of energy saving and other features relating to the emerging technology of Electric vehicles, the R & D efforts on this project were concentrated on Integrated Electronic Control Systems. The electronic Controls for current range of vehicles and future electrical vehicles are based on electrical motor control using inverters (A.C. Motor Drives) or choppers, (for D.C.Motor Drives), and continuous effort on making them energy efficient is being committed by many countries. Compared to conventional systems the electronic control systems are much more precise in their operation and do not involve moving parts with inherent wear and tear. In addition to this electronic control devices are highly energy efficient.

- 6. Use of variable frequency three phase solid state A.C. Motor drives for Traction applications has steadily grown during the last decade largly due to the development of high power inverter grade semiconductor devices. These drives will also be useful for other requirements of drives used in process control industry. The ideal drive for these applications is a micro processor based PWM AC Drive. Such a drive when developed will cover very wide range of applications, because of the inherent Software Control available with Microprocessor based systems.

\_ 4 \_

- 7. These high efficiency drives require Application Specific Integrated Circuits (ASICs) to perform brain functions (i.e. Logic & Control) Power Transistors to perform muscle function (i.e. driving the motor) and Hybrid microcircuits to provide intermediate links.

- The project envisaged the development of application specific integrated circuits, Power Transistors, Hybrid microcircuits and Solid State AC Drives.

The development objective and immediate objectives were defined in the project document as follows:

A. Development objective:

.

Ð

The development objective of the project is to promote the utilisation of electronic systems for transportation by increasing the operational efficiency of electric vehicles and to achieve a self-reliant product development capacity in this field.

B. Immediate objectives: \*

The immediate objectives of the project are:

- (i) Development of <u>power transistors</u> for power control in electric drives for transportation.

- (ii) Development of <u>custom</u> <u>designed</u> <u>monolithic</u> <u>integrated</u> <u>circuits</u> <u>especially</u> for use in transportation

\* Same as per original proposal

- (iii) Development of hybrid integrated modules for especially control of electric drives for transporation.

- (iv) Development of Silid State AC Motor Drives and System packages to suit the requirement of transportation, including electrically driven vehicles.

- 9. The objective of the project were conceptualised to be achieved in the following stages.

- (i) Conceptual paper design of system packages Integrated Circuits, Power Transistors and Hybrid Microcircuits (using CAD wherever applicable).

- Implementation of design and iteration. (ii)

- (iii) Prototype development,

- (iv) Batch fabrication of semiconductor devices.

- (v) Testing of the semiconductor devices independently and in the system package.

### III. ACTIVITIES CARRIED OUT AND OUTPUTS ACHIEVED

10. Based on the main activies outlined in the project detailed work plan was prepared in May 1985. document, This work plan contained the major activies as given in the project document and subactivities with their estimated date of start and duration of the activities.

The work plan was reviewed periodically by the project Director, in 6 monthly progress reports, and by PAC and TPR. Depending upon the external constraints target dates of the activities were revised so as to correspond to

These activities were carried out through the project personnel, UNDP provided expert/consultants and UNIDO assistance. A brief account of the activities according to which the project was implemented are given below:

- a.

- **General Activities**

- Preparation of detailed work plan for implementation of i) the project.

- ii) Budgetary provision and assignment of national staff to provide counterpart inputs.

- iii) Identification of International Consultants and making arrangments.

- Identification of sources of supply of equipments based iv) on the Formulation of specifications, prepared through detailed technical discussions.

- Identification of places for fellowship training. V)

- Arranging PAC and TPR meetings and preparation of notes vi) for discussion in these meetings.

- Interaction with UNDP/UNIDO, CSIR and DEA in relation vii) to project implementation.

- b. **Project Activities**

Placement of orders for the equipment. **i**)

ii) In consultation with CSIR and UNDP a Project Advisory Committee (PAC) to monitor the progress and to guide on the implementation of the project was constituted. The constitution and terms of reference of the PAC are given at Annexure I. The action taken on the recommendations of PAC are given in Annexure XV.

- 8 -

- iii) <u>Coordination of Specifications of Devices</u> and system. After drawing the specifications of the system the input output parameters and other specifications of power transistors, hybrid circuits, and monolithic integrated circuits were evolved, through brain storming sessions and periodic discussions with experts.

- iv) The above conceptual specifications were discussed among project personnel and consultants and design rules etc. were prepared.

- v) The project was carried out basically through the following stages.

- a) Design of the system, sub-systems and devices (using CAD wherever applicable).

- b) Processing the devices

- c) Testing the devices/sub-system

- d) Iteration.

- 11. The availability of the project personnel was adequate (Necessary internal mobilisation of personnel was done wherever required). The consultants/experts were available for the project. The consultants helped the project in defining the design parameters more accurately, designing and processing. Some of the consultants accepted the project personnel for fellowsip training also assisted in design and processing of monolithic and integrated circuits (Prof. P. Jespers, UCL Belgium). Out of a provision 23.7 m/m of consultant 22.3 m/m have been utilised. The list of the experts is given in Annexure - II. The action taken on the recommendations of UNDP consultants is given in Annexture XIV.

- 12. A list of the scientific and technical personnel of Central Electronics Engineering Research Institute is given at Annexure -III.

- 13. 18 Project personnel received fellowship training abroad at Centres of higher learning and technology. Three study tours by National Expert, Project Director and Area Coordinator, Semiconductor Devices Area were undertaken. The details are given in Annexure IV and V. The fellowship programme was specific and involved the fellows working actively on ongoing research programmes.

Two of the fellows, e.g. Dr. Chandra Shekhar and Sh. OP Wadhawan, designed and processed the two IC chips at UCL Belgium.

## 14. Procurement of Equipment

The procurement of equipment was carried out by UNIDO and CEERI. The equipment procured under UNDP funds and counterpart funds is given at Annexure VI and VII respectively. The total equipment (expendable and nonexpendable) procured under UNDP was of the order of \$ 1,257,072. Some comments on the implementation of equipment procurement are give below:

Prior to sending requisition on major pieces of equipment, the project management carried out preparatory work of identification of equipment meeting the desired specification and possible vendors.

- ii) Most of the equipments were commissioned either directly by project personnel or with the help of vendors' representatives/Engineers.

- iii) One piece of equipment i.e. Cold Wall Vacuum furnace could not be commissioned till date. The supplier of the equipment also was not cooperative enough to help the Institute in sorting out problems of this equipment inspite of continuous follow up and sustained efforts of the Project personnel & UNDP officers. The non-commissioning of this furnace has delayed the delivery of the out put.

- iv) Another piece of equipment Laser Trimming System could be commissioned by the vendors only after two years and it worked upto the specifications only for less than two months. All efforts to pursuade the vendor for providing warranty service have failed.

- v) The position of procurement of expendable equipment was satisfactory except for the above two cases, for which alternative arrangements through outside assistance had to be made by the Institute. The authorisation for field purchase were very useful.

- vi) The following two cases of procurement have caused considerable delay in implementation of the project.

Procurement of 300 Amps. power transistors. The first indent for this purchase was raised in 1984, but these items of expendable equipment could not be procured. A few pieces would be procured through counter part funds only by the end of 1987. This resulted in delays for the assembly and testing of the system module. A respective equipment requisition was sent to UNIDO in February '88. Goods were ordered and shipped on 9 December 1988.

- vii) The order for the procurement of packages for 300A transistors were placed mid-February '88. The delivery of goods, however, has been delayed very much thereby affecting the project progress.

- 15. The interation with Project Advisory Committee, Experts/Consultants, Indian Industry, Department of Electronics, Govt. of India and other agencies helped in the project implementation. The scientific and technical work of the project to meet the outputs was carried out under four different groups, viz (A) Power Transistors;

(B) Monolithic Integrated Circuits; (C) Hybrid Integrated Modules:

(D) Solid State AC Motor Drives and System Packages.

Continuous interaction between groups was established through day-to-day working level contact and periodic meetings arranged by the Area Coordinator and Project Director and Project Leaders associated with the project teams. - 12 -

- 16. A note on the <u>nature of the products and processes developed</u> <u>under the UNDP Project is placed at Annexure VIII.</u>

- 17. The details regarding Hard and soft out of the four groups of the project are given at Annexure IX.

- 18. A list of engineers/scientists trained within the country is given at Annexure X.

- 19. The details regarding linkages established with the industrial organisations are given at Annexure XI.

- 20. The details of International collaboration in the subject areas covered under the UNDP project are given at Annexure XII.

- 21. The list of Seminars/Symposia/Workshops etc. arranged at CEERI is given at Annexure XIII.

## A. DEVELOPMENT OF 100 AND 300 AMPERE DARLINGTON POWER TRANSISTORS

### (i) INTRODUCTION:

The recent addition of GTOS, Darlington Power Transistors and Power MOSFETs to the existing families of Bipolar Junction Transistors (BJTS) and thyristors have widened the choice for the selection of power switches for solid-state power control involving inverters and converters. At the same time, further developments in these original power switching devices to give them a competitive performance have added a new dimension to the power electronics field. In the low and medium power applications Power Transistors have started replacing thyristors because of their inherent advantages such as

- a) Lesser number of power devices required compared to thyristor control because no commutation is required with transistors for turning them off.

- b) Higher switching speed.

- c) Lower losses and lower EMI problems.

- (ii) Accordingly, in the development programme under UNDP Power Darlington Transistors were taken as intrinsic components for AC Motor Drives. At higher power rating, the current gain of an individual power transistor is low. Larlington configuration overcomes this problem to a larger extent due to its higher gain at high currents and it is widely accepted in PWM AC Motor drives for electric vehicles.

"CAD" as a tool has been used to design 100A and 300A Darlington Transistor. A separate design report on this has been submitted, which constitutes one of the important outputs of this project. The approach uses "Bipole" programme which has been equipped with physical models of heavy doping, base widening and emitter crowding effect and is capable of analysing the device laterally and vertically. Results obtained using CAD approach (Table AI) show that it is desirable to use thin emitter fingers which again reduces the effective emitter area, that is the silicon size for same electrical characteristics.

#### TABLE Al

÷ 1

SIMULATED RESULTS FOR JOMAX AND CROWD FACTOR (Composite gain and current Ic for device under study)

| Jcmax<br>A/cm2 | tuu<br>I | B<br>CM | hrs   | IC.<br>A | Vbe<br>VOLTS | CROWD  |

|----------------|----------|---------|-------|----------|--------------|--------|

| <br>79         | 650      | 64      | 10.0  | 40       | 0.826        | 0.50   |

| 68             | 550      | 25      | 10.7  | 47       | 0.845        | 0.59   |

| 41             | 350      | 66      | 9.6`` | 74.6     | 0.803        | 0.80   |

| 23             | 250      | 64      | 10.3  | 35.8     | 0.747        | 0.90   |

| 22             | 200      | 16      | 10.2  | 7.5      | 0.736        | · 0.93 |

| 16             | 150      | 64      | 10.2  | 17.0     | 0.718        | 0.99   |

| 85             | 4000     | 10      | 12.0  | 20.0     | 0.800        | 0.20   |

#### COMPOSITE DARLINGTON TRANSISTOR

| Jcmax | Comp.hm | Ic  | Vbe  | CROWD |

|-------|---------|-----|------|-------|

| 80    | 107.30  | 183 | 0.99 | 0.56  |

| 90    | 97.12   | 196 | 1.04 | 0.55  |

| 100   | 90.40   | 205 | 1.12 | 0.54  |

|       |         |     |      |       |

- 14 -

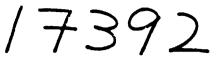

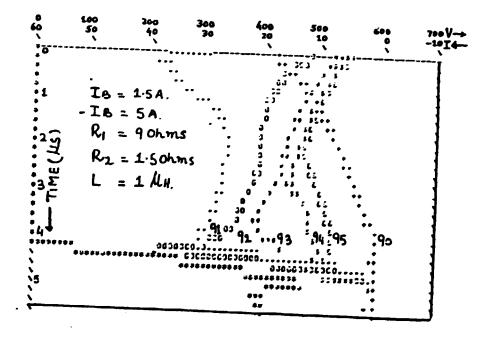

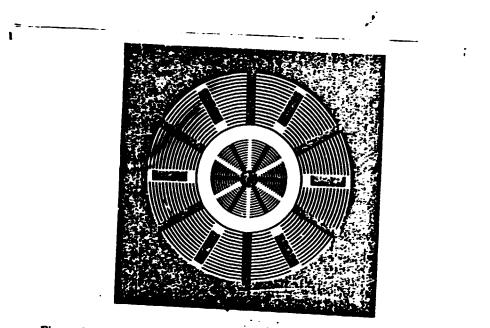

Based on CAD results, it has been possible to make emitter layout for the device. In the first stage, 100A transistor layout has been made as shown in Fig. Al. This single emitter geometry has emitters for input transistor T2 (Driver transistor) and output transistor T2 (output transistor), the emitter segments of output transistor T2 having p-layer region form a free wheeling diode 'D°. These different regions T1 ,T2 and °D' have been connected through in-built diffused resistors R1 and R2 (which are formed on Metallization). Both input and output emitter segments have been made on single layout, to ensure same peak gain and breakdown voltage for both transistors. For ease of phtomasking, emitter fingers have been made little wider than computed finger width, to check the feasibility of design approach.

Fig. A1 Actual Emitter Geometry of 100 A Darlington Transistor.

- 15 -

## IV. Devices Simulation for network analysis:

"WATAND' program has been used to study the theoretical switching behaviour and  $h_{fe} - I_c$  variation, under different load conditions, of the designed transistor. It was noted in relation to the proposed application for AC Motor drives that most critical condition for this operation is inductive load therefore emphasis has been put to analyse the device during turn-off, with inductive load.

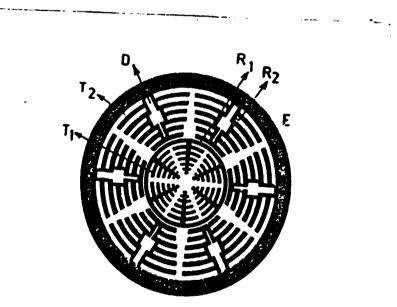

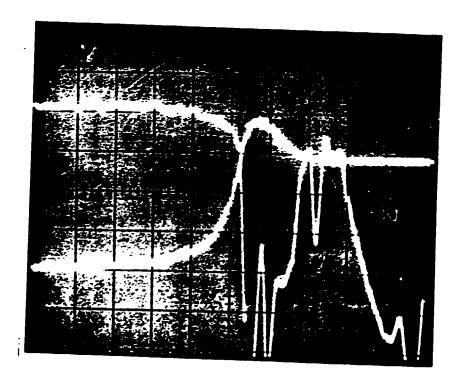

During inductive turn-off Darlington transistor must pass from the filly "on" stage to the "off" state as quickly as possible to minimize power loss. The ability of the device to withstand such current and voltage stresses during inductive turn-off is defined as RBSOA. To predict such ability of device, "WATAND" network circuit for inductive load is used as shown in Fig.A2.

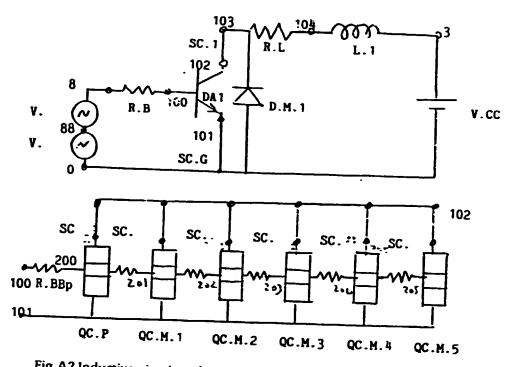

In simulation study, it is assumed that device is already in the 'on' state and each section of emitters of the developed device is divided into five individual sub-sections. Simulated behaviour of current with time in these five sections of output collector transistor is illustrated in Fig.A3. It is found from such other simulated results that with increasing magnitude of reverse base current, the current focussing in the centre region just under emitter is enhanced and thus increases the temperature in that local region which makes device unstable. For present device the current density up to 87A/cm2 is obtained in simulation results while for initiation of "RBSB" the essential current density should be of the order of 160A/cm . This implies that even under large reverse base current . power dissipation across Darlington transistor is not high enough as the product of  $V_{cs}(t)$  and  $I_{c}(t)$  at any time lies in the region bounded by  $V_{cE}$  and  $I_c$ , as predicted by Bipole programme.

Fig. A2 Inductive circuit and sectioned representation of Darlington Transistor used in WATAND transient analysis.

Fig. A3 Computed current variation with time in different emitter sections under inductive load condition.

vi. Based on approximate geometry, using CAD design approach, the physical and electrical parameters of 100A Darlington transistor have been tabulated in Table-AII.

- 18 -

CAD studies on 100A transistor have been extended to 300A transistor design and so upscaling of 100A emitter layout has been done to make emitter geometry for 300A transistor. The upscaled 300A emitter geometry as shown in Fig.A4, consists of dual base contact for fast recovery.

Fig. A4 CAD based geometrical layout of 300 A Darlington

1

-

-

.

•

.

•

.

| TAB | LE | AII | [ |

|-----|----|-----|---|

|     | •  | ••• | _ |

| Physical Parameter             | r                                               | Electrical Characte                                                                                                                 | ristics   |

|--------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------|

| ND                             | 10 <sup>14</sup> /cm <sup>3</sup>               | Composite h <sub>re</sub><br>(V <sub>CE</sub> = 5 Volt                                                                              | 100       |

| Epi thickness                  | 85 um                                           | I <sub>C</sub> = 100 A)<br>V <sub>CE sat</sub><br>(at I <sub>C</sub> = 100A)                                                        | 1.9 Volt  |

| Substrate Conc.                | 10 <sup>19</sup> /cm <sup>3</sup>               | v <sub>сво</sub>                                                                                                                    | 856 Volt  |

| X <sub>j</sub> N <sup>+</sup>  | 9 µm                                            | h <sub>fE1</sub>                                                                                                                    | 16        |

| Х, +<br>јр                     | 22 µm                                           | h <sub>fE2</sub>                                                                                                                    | 8.6       |

| w <sub>B</sub>                 | 13 µm                                           | V <sub>CEO</sub>                                                                                                                    | 625       |

| w <sub>C</sub>                 | 63 µm                                           | V<br>CEO sus                                                                                                                        | 500 Volts |

| <sup>о</sup> в/о <sup>в</sup>  | 1.185x10 <sup>12</sup><br>cm <sup>-4</sup> sec. | <sup>t</sup> on<br>(I <sub>C</sub> =100A,                                                                                           | 1.2 usec. |

| о <sub>в</sub> -               | 2.37x10 <sup>13</sup>                           | $V_{CC} = 400 \text{ Volt,}$<br>$L = 10 \ \mu\text{H}$ )<br>$t_{off}$<br>$(I_{C} = 100 \text{ A,})$<br>$V_{CC} = 400 \text{ Volt,}$ | 8 usec.   |

| <sup>Ae</sup> 1                | 0.4879 cm <sup>2</sup>                          | L = 10 µH)<br>h <sub>fEO</sub> at 50 A                                                                                              | 300       |

| Ae <sub>2</sub>                | 3.002 cm <sup>2</sup>                           |                                                                                                                                     | _         |

| R <sub>1</sub>                 | 9 ohms                                          |                                                                                                                                     |           |

| R <sub>2</sub>                 | 1.5 ohms                                        |                                                                                                                                     |           |

| Q <sub>E</sub> /D <sub>E</sub> | $4 \times 10^{13}$ cm <sup>-4</sup> sec.        |                                                                                                                                     |           |

I.

.

### - 20 -

# Fabrication of Monoloithic Darlington Transistor:

# VII. Fabrication Facility Set Up

On completion of designed emitter layout the fabrication facility for large area power devices, has been initiated. The planar device structure has been used for the fabrication of the following 100A and 300A Darlington transistor and therefore facilities for different fabrication processes have been established:

- A. Sealed tube deep diffusion

- B. Bevelling and contouring

- C. Spin Etching

**. . .**

- D. Pyrogenic Oxidation

- E. D.C. and A.C. measurement set up

# a) <u>Sealed tube deep diffusion:</u>

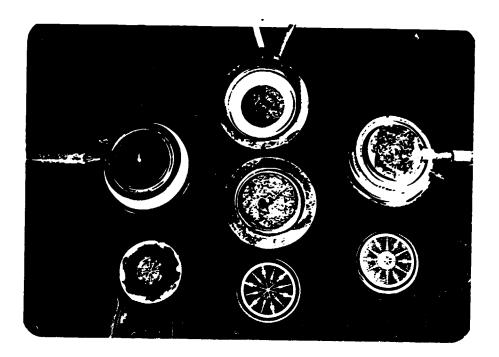

Initial set up for diffusion has been replaced on procurement of VHS-6 Varian Vacuum System under UNDP Programme. To initiate deep diffusion for large area devices up to 3" a sealing adaptor for holding quartz capsule, was locally fabricated. Such a facility is a basic requirement for high voltage devices. Elemental gallium as ptype impurity has been used for deep diffusion because of its high diffusion  $\infty$ -efficient and low mismatch factor with silicon lattice. In sealed tube diffusion, uniform spread in sheet resistance and high lifetime have been achieved and large number of wafers  $\gamma$ ould be diffused. Photograph  $^{\circ}AI^{\circ}$  shows complete set up for sealed tube deep diffusion for high voltage junctions, commissioned by the CEERI project team.

Photograph 'A1' Sealed Tube Deep Diffusion

Phograph 'A2' Bevelling and Contouring Equipment

1

### b) Bevelling and Contouring:

Planar structure has its limitations for high voltage junction due to the curvature effect It is very essential to control or shape the surface so that depletion region could be extended and does not tend to terminate at the surface. In present planar structure therefore shaping of the surface of p-n junction has been introduced to achieve high breakdown voltage. Bevelling and contouring set up is shown in Photograph 'A2'. This set up has been utilised for sand blasting the peripheral damages which occur in alloying and laso used for bevelling the p-n junction at particular angle to avoid premature surface breakdown and to achieve high bulk breakdown voltage. The speed of the wafer, charge quantity, pressure and the angle of contour have been optimised for required purpose to get high breakdown voltage of the transistor.

### c) Spin Etching of Bevelled Junction:

The bevelled surface of p-n junction has the damaged surface after bevelling and it gives rise to large junction leakage. It is essential to get a damage free and smooth surface to support high breakdown voltage with minimum junction leakage current. In this regard, a spin etching technique has been introduced to chemically etch bevelled surface without deteriorating the metallised E-B regions of the transistor. Spin Etch Set-up is shown in Photograph 'A3' System holds the transistor fusion and rotates it at the required speed and acid jet sprays the chemical to etch the surface. Speed of rotation, flow of etchant, etching angle and time have been optimised for its proper function. The smooth damaged free surface has been obtained which suports the high voltage.

- 22 -

Photograph 'A3' Spin Etching Equipment

Photograph 'A4' Pyrogenic Oxidation System

Photograph 'A5' Measurement Set-up

## d) Pyrogenic Oxidation:

The fabrication of high voltage transistor requires high minority carrier lifetime in p and n base of the transistor. Wet oxidation and thermaltreatments of silicon wafer deterioprates the minority carrier; life time due to heavy metal impurities in D.I. water cleaning chemicals and thermal stresses. Pyrogenic oxidation as a process, used hydrogen and oxygen for steam at high temperature. This process is cleaner and it yields low oxide charge and uniform oxide thickness. Phot.graph 'A4'shows established pyrogenic oxidation system. For pyrogenic oxidation special hydrogen injection has been fabricated in house at CEERI. It injects H at 700 - 800 C and oxygen at the end of the opening in required ratio so that any explosion in tube can be avoided.

### e) Measurement Set up

Measurement set up as shown in Photograph 'A5' has been commissioned to measure breakdown voltages, gain characteristics, V CESAT V , R ,R and switching parameters of the transistor.

#### VIII. Fabrication Process of 100A and 300A Transistor:

The process developed at CEERI for fabrication of 100% and 300A transistor uses epitaxial wafer non n high breakdown and for low saturation voltage. Transistors have been fabricated using epitaxial double diffusion process. The alloyed fusions are mounted into a compression type package. The developed monolithic Darlington transistor has planar emitter-base; hence Ni-plated molybdenum preform for emitter contact has been introduced. The developed 100A transistor with different stage and its packaged version has been displayed in Photograph 'A6'.

- 25 -

•

Photograph 'A6' Packaged 100A Transistor with Different Stages

.

The 300A monolithic darlington transistor has also been developed but it can be fully tested only after the availability of dual base packages. The fabrication steps involved in their development are shown in Fig. 'A5'.

# IX. Test Results and User's Trials

The developed 100A transistor has been checked and the results obtained meet the required specifications for its use in A.C. Motor drives. The transistors have been checked by internal users in the Power Electronics Systems and their results are shown in Table-III. The testing of 100A transistor under inductive load condition has been done. The Photograph A-7 shows the behaviour of I and V during turn-off condition.

PHOTOGRAPH 'A7' Variation of I and V during inductive turn-off.

## TABLE-III

- 29 -

# TEST RESULTS ON CEERI DEVELOPED DARLINGTON TRANSISTORS

TEST CONDITIONS

•

\_

Base Drive Power Supply =  $\pm$  8V

| Vcc                                                          | = 150 | v    |      |      |      |      |      |      |       |

|--------------------------------------------------------------|-------|------|------|------|------|------|------|------|-------|

| Serial No.                                                   | 1     | 2    | 3    | 4    | 5    | 6    | 7    | 8    | UNIT  |

| Base-Emitter Resistance                                      | 15.0  | 14.5 | 16.0 | 16.8 | 15.0 | 16.9 | 1.6  | 1.5  | ohms  |

| ON CHARACTERISTICS:                                          |       |      |      |      |      |      |      |      |       |

| V <sub>8</sub> (Sat)                                         | 1.4   | 1.5  | 1.5  | 1.3  | 1.4  | 1.5  | 1.35 | 1.35 | Volts |

| +ve Base Current                                             | 1.4   | 1.4  | 1.45 | 1.4  | 1.4  | 1.4  | 1.55 | 1.60 | Amp.  |

| -ve Base Current                                             | 0.4   | 0.45 | 0.4  | 0.4  | 0.5  | 0.3  | >0,5 | >0.5 | Amp.  |

| Collector Current (IC)<br>(As which the device<br>is tested) | 70    | 76   | 70   | 72   | 80   | 70   | 70   | 70   | Amp.  |

| V <sub>Cf</sub> (sat) at<br>above test current               | 0.8   | 0.9  | 1.1  | 1.2  | 1.3  | 1    | 1    | 1.2  | Volts |

| Sl.No.                                              | 1      | 2      | 3              | 4     | 5      | 6         | 7       | 8   | UN       |

|-----------------------------------------------------|--------|--------|----------------|-------|--------|-----------|---------|-----|----------|

| SWITCHING CHARACTERIS                               | STICS: |        |                |       |        |           |         |     |          |

| (a) R-L Load (Vcc<br>Storage time (t <sub>5</sub> ) |        |        |                |       | -      | 7.5       | 7.0     | 8.0 | μs       |

| Fall time(t;)                                       | 1.4    | 1.5    | 1.5            | 2.0   |        | 1.5       | 1.5     | 2.0 | μs       |

| (b) Resistive Load (                                |        | , IC = | 80 Amg         | ; tes | ted fo | or one o  | device; | )   |          |

| Delay Time (は)                                      | 0.2    | , IC = | 80 Amg         | ; tes | ted fo | or one (  | device; | )   |          |

|                                                     |        | , IC = | 80 Amg         | ; tes | ted fo | or one of | device; | )   | μs<br>   |

| Delay Time (は)                                      | 0.2    | , IC = | 80 Am <u>r</u> | ; tes | ted fo | or one o  | device; | )   | צע<br>גע |

.

· ·

- 30 -

. .

- 31 -

# B. MONOLITHIC INTEGRATED CIRCUITS

- Application Specific Integrated Circuits (ASICs) are rapidly X) becoming the key microelectronic components in realising any modern electronic system. They provide a compact, low power, high performance, cost effective and reliable alternative to the use of standard SSI and MSI circuits. The "brain" prtion of a modern microprocessor based electronic system can be functionally partitioned into several ASICs including  $\infty$ processor and other components. The ASIC chips and microprocessor software are then developed to realise the system.

- xi) In line with the above approach, the following objectives were set for the microelectronics activities under this project.

- (a) Design of a VME-Bus compatible controller for multichannel analog data acquisition [here after referred to as chip 1].

- (b) Development of 6 micron NMOS process technology and fabrication of chip 1.

- (c) Design of a dedicated 16-bit co-processor for the generation of Pulse Width Modulation Pattern of inverter controlled A.C. Motor drives.

- (d) Validation of this design through chip fabrication at a suitable foundry and iteration.

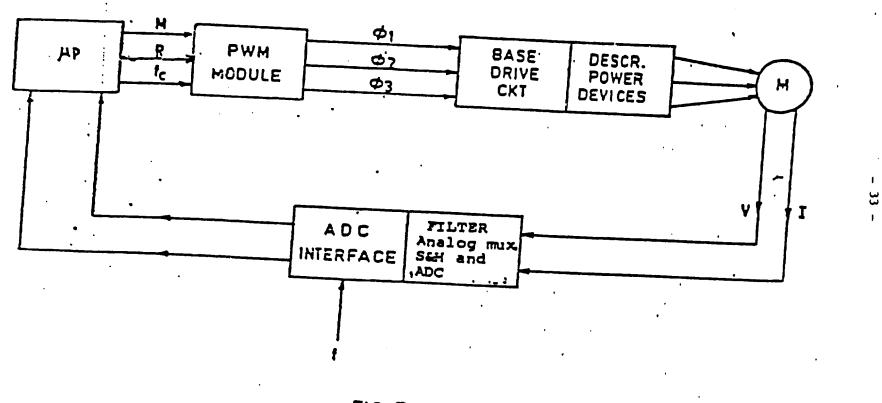

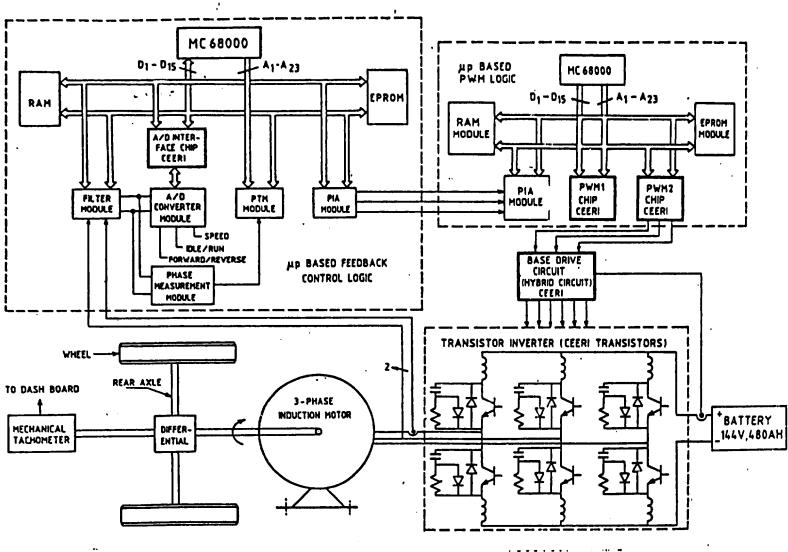

A functional block diagram of the system showing the roles of these chips is shown in Fig. Bl. - 32 -

# xii) Identification of ASICs :

- a) The implementation strategies for Pulse Width Modulation (PWM) control of A.C.Motor drives were jointly examined and debated by system designers and VISI designers. It emerged from these discussions that there were two distinct sub-tasks for which ASICs could be most gainfully designed.

- b)

- The first of these tasks was the interfacing of analogue feedback signals (such as instantaneous voltage and current, transformed into digital signals) from the motor to the microprocessor. An ASIC for this purpose would simplify system design and significantly reduce the total chip count of the system. It was, therefore, decided to design a VME bus compatible controller chip for multichannel analog data acquisitions (chip 1). It should be noted here that since Motorola 68000 was chosen as the CPU for the system, this VME bus compatible chip was so designed as to be useful to all similar 68000 based micro computer controled systems.

- c) The other task was the repetitive, computation intensive, time critical task of calculating modulated pulse widths and generating the PWM signals in real time. Analysis showed that the microprocessor component of the system would spend most of its time doing the above task, and infact, would not be able to cope up with this task beyond a certain switching frequency - thus limiting the range of output frequencies and harmonic purity of the inverter drive.

d) It was, therefore, decided to develop a 16-bit PWM processor that would take over this task from the microprocessor relieving the associated frequency constraints from the AC drive and freeing the microprocessor for other system tasks.

### xiii) Design

# <u>VME bus compatible controller for multi-channel analog data</u> acquisition (Chip 1).

- a) This chip was designed by the VLSI design team at CEERI using the Applicon AGS-860 interactive graphics system and the circuit simulator MSINC running on HP-1000 computer. The design was based on CEERI's own inhouse 6 micron NMOS technology rules (design rules).

- b) The chip is designed to accept a channel number for analog data acquisition from the microprocessor via the VME bus. It then generates the necessary sequence of control signals for the analog multiplexer, sample and hold circuit, and Analog-to Digital converter to initiate data conversion on the channel. The status of conversion is monitored by the chip and the microprocessor is interrupted when conversion is complete. The chip then identifies itself to the microprocessor during the interrupt acknowledge cycle and then sends over the acquired digital data from the channel to the microprocessor.

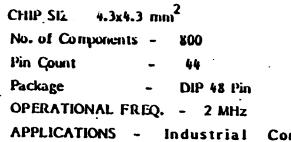

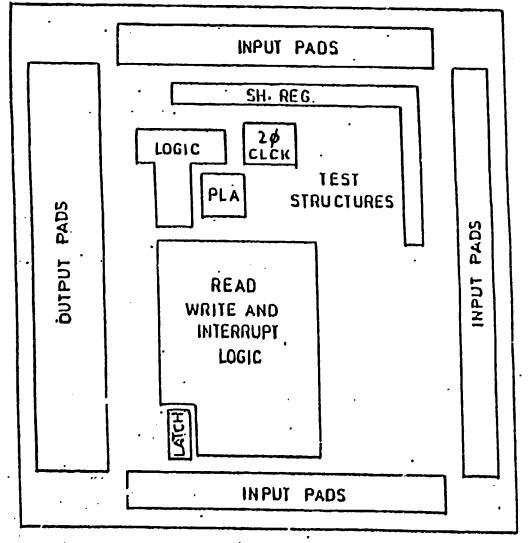

Chip No.1 : VME Bus Compatible Controller Chip for Multichannel Analogue Data Acquisition

- c) Special pin programmability features permit the chip to control practically any analog multiplexer, sample and hold and Analogto Digital converter circuits and thus interface them to the microprocessor via the VME bus. Masks for this design were made inhouse by the mask making team using the Electromask - 250 Combo pattern generator and image repeater machine.

- d) Chips were also fabricated inhouse using the 6 micron NMOS process technology. Packaged chips were successfully tested against all the design specifications and samples of chips have been made available to the system designers.

- e) A detailed technical report on the design is available. The design details were also published in an international journal. A picture of the chip and a summary information on its transistor count, pin count, power consumption, maximum clock speed etc. are given in Fig. B2 and Table BI.

- xiv) Design of a dedicated 16-bit PWM Processor (Chip 2 and Chip 3)

- on discussions with the a) Based system designers, broad specifications of this chip set were worked out during the consultancy visit of Prof. P. Jespers to CEERI. Since the estimated chip complexity was beyond the capability of Computer Aided Design (CAD) tools and wafer fabrication facilities at CEERI, Prof. Jespers offered the use of CAD tools and wafer fabrication facility at his laboratory - labo. microelectronique, Universite' Catholique de Louvain, Belgium for the development of these chips.

- 37 -

(Acts as a multichannel data acquisition controller in VME Bus based systems)

Industrial Control-Instrumentation & Systems

FLOOR PLAN .

.

FIG.B2.

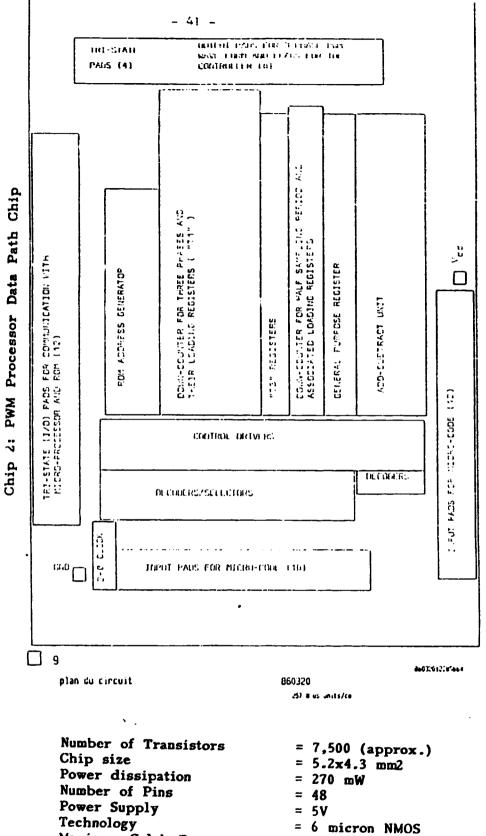

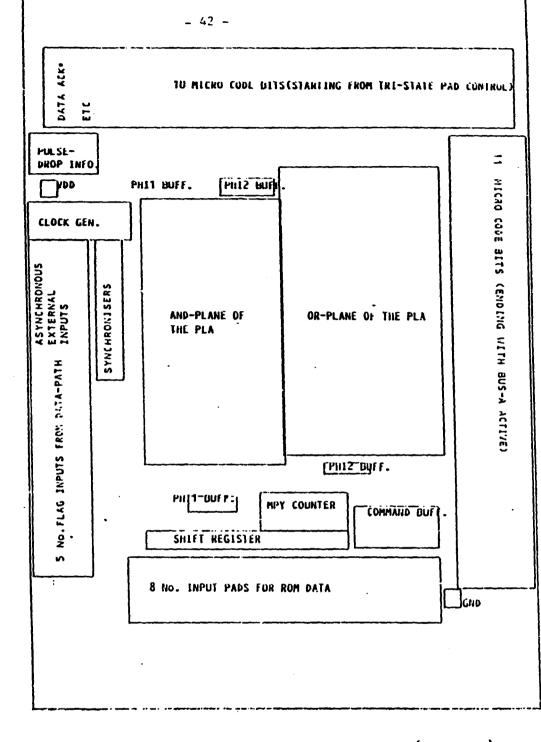

- b) Accordingly, the set of two chips namely the PWM Data Path chip (chip 2) containing about 7500 transistors and the PWM controller chip (chip 3) containing about 3000 transistors which together constitute the dedicated 16-bit PWM processor were designed by a VLSI designer from CEERI during the tenure of his UNDP fellowship at UCL, Belgium.

- c) These chips accept the four parameters (namely A.C. output frequency of the inverter, frequency ratio, modulation index, and minimum pulse width for pulse retention) that characterise the PWM signals from the host microprocessor. Using these and the sine function samples from a ROM, the chips execute one million operations per second to compute and generate the three phase PWM signals for inverter control.

- The PWM processor can handle any of the popular sampling d) techniques e.g. regular symmetric, regular asymmetric, averaging and constant area based. based It can support output frequencies from 1 Hz to 300 Hz using frequency ratios that are odd multiples of three in the range of 3 to 45. (It may be noted that these limits cover a wide range of applications of PWM AC Motor drives used in Transportation and Industry) The output voltage level of the inverter can be controlled in 128 steps. The processor also handles overmodulation and pulse dropping which are often required to achieve the full voltage capability of the inverter. The processor can control inverters designed with different kinds of switching devices meant for different power levels.

- 38 -

Masks for chip 2 and chip 3 were fabricated by a commercial mask house and chips were fabricated at UCL, Belgium. Packaged devices were tested at CEERI. As no VLSI tester was available at CEERI, special test setups and cards had to be developed to test the chips. This did cause delays in the testing of the chips.

- e) Results of testing established the correctness of design of chip 2. However, a defect in the mask (caused during mask handling) had caused malfunctioning of a very small portion (one register) of this chip. It, therefore, became necessary to repeat mask fabrication and chip fabrication for this design.

- f) Testing of the FWM controller (chip 3) showed that there was a design error (wrong interconnection in the feed back part of the main finite state machine ) in that chip. Redesign of this chip was carried out at CEERI using the Applicon AGS-860 interactive graphics system and a specialised CAD tool (NMOS PLA based silicon compiler for finite state machines) developed at CEERI.

- g) Mask fabrication at a commercial mask house and chip fabrication at UCL, Belgium for these cnips (chip 2 and chip 3) would be completed by Nov./Dec. 1982. Simultaneously, a mask set for the modified design of chip 3 is presently being fabricated inhouse and its chip fabrication at CEERI would commence shortly.

- 39 -

A detailed technical report on the design of the PWM processor is available. Part of the design details were presented at a technical conference. Block diagram of the PWM data path and controller chips together with their transistor counts, pin counts, maximum frequencies of operation and power consumption etc. are given in Figs.B3 and B4.

#### xv) Development of Silicon Gate NMOS Technology

Development of silicon gate NMOS process technology for the fabrication of integrated circuits, was initiated with the help of UNDP experts. The effort was started with the help of test masks designed at CEERI. This set of masks contained the following test structures.

- a. Enhancement mode transistors

- b. Depletion mode transistors

- c. Field transistors

- d. Inverters with depletion and enhancement load

- e. Ring Oscillators with depletion and enhancement load

- f. Step coverage patterns

- g. Alignment monitoring structures

- h. Structures for different layers

- i. Capacitors

- j. Contact characterisation structures

The detailed report on these structures was also prepared. The process evaluation using these masks helped to standardise various process parameters. The tolerances on these parameters were determined by collecting statistical data on wafers from

- 40 -

- Technology Maximum Colck Frequency

- = 1.5 MHz

!.

| Number of Transistors   | 2   | 3000 (approx.)          |

|-------------------------|-----|-------------------------|

| Chip size               | =   | 3.3x3.2 mm <sup>2</sup> |

| Power dissipation       | =   | 120 mW                  |

| Number of Pins          | =   | 43                      |

| Power Supply            | 3   | 5V                      |

| Technology              | × · | 6 wicron NHOS           |

| Maximum Clock Frequency | ' = | 1.5 MIZ                 |

Chip 3 : PWM Processor Controller Chip

different process runs. The design rules were then evolved. These are given in Table C.I. The details of technology developed were published in an international journal (Annexure VIII).

# xvi) Chip Fabrication

Bus compatible controller chip for multichannel VME analogue data acquisition, was fabricated using the above mentioned process technology. Various threshold voltage were checked on test devices. The constituent cells of the circuit i.e. PLA, shift register, clock, super buffer, delay element with lat hes were also tested on the wafer. The good chips were diced out, inspected and encapsulated in 48 lead ceramic dual in line package. Functional testing of the circuit which was later done on encapsulated chips met the all the design specifications.

#### TABLE B.1

#### DESIGN RULES

# SILICON GATE NMOS TECHNOLOGY

| Enhancement threshold                        | -     | 1 <u>+</u> 0 | .2 V        |

|----------------------------------------------|-------|--------------|-------------|

| Depletion threshold                          | -     | -3 t)        | 3.5 V       |

| Field threshold                              | -     | 15 -         |             |

| Minimum feature size<br>(contact on level 7) | -     | 6 X 6        | 2<br>micron |

| Minimum diffusion width                      |       | -            | 8 micron    |

| Min. Diff. to Diff. separ                    | atior | n –          | 8 micron    |

| Minimum poly width                           |       | -            | 8 micron    |

| Min. poly to poly separat                    | ion   | -            | 8 micron    |

- 43 -

| Min. metal width                 | - 10 mici   | on  |                     |

|----------------------------------|-------------|-----|---------------------|

| Metal to Metal separation        | - 10 micu   | ron |                     |

| Min. Metal to Diffusion separat  | ion/overlap | -   | 2 micron            |

| Min. Metal to poly separation/o  | werlap      | -   | 2 micron            |

| Min Diffusion to poly separation | n           | -   | 4 micron            |

| Poly overhang in Transistors     |             | -   | 5 micron            |

| Contact on level 6               |             | -   | 2<br>8 x 8 micron   |

| Diffusion/Poly extension around  | contact (7) | -   | 4 micron            |

| Metal extension around contact   |             | -   | 2 micron            |

| Butting contact a) Level         | 6           | -   | 2<br>16 x 10 micron |

| b) Level                         | 7           | -   | 2<br>12 x 6 micron  |

| Diffusion poly overlap for butt  | ing contact | -   | 2 micron            |

| Implant extension around         | ٩           |     |                     |

| Depletion Transistor areas       | ۲<br>۱      | -   | 6 micron            |

| Separation between depletion im  |             |     |                     |

| and enhancement transistor       | 9<br>1      | -   | 6 micron            |

# xvii) Achievements :

- VME bus compatible controller chip for multichannel analog data acquisition (chip 1) successfully designed, fabricated and tested.

- 2. Silicon gate NMOS technology successfully developed.

- 3. Design of the PWM processor's data path chip (chip 2) successfully completed and validated through the testing of . fabricated chips.

Design of the PWM processor's controller chip (chip 3) debugged through testing of the fabricated chips. Design modifications completed and refabrication initiated.

Chips from the modified designs expected in Nov. -Dec. 1988 would be made available to these users besides inhouse users for developing prototype systems.

#### xviii) Any other Relevant Point :

Based on the design expertise gained through this project, Deptt. of Electronics (Govt. of India) has funded the setting up of a VLSI Design Centre for Industrial ASICs at CEERI. Under this project, Deptt. of Electronics would provide grants to strengthen CAD facilities at CEERI and CEERI will design chips for industrial applications besides software CAD tools. A serial Data Communication Controller Chip for C-DoT is presently being developed besides another in-house chip.

A mutually benefitial bilateral R&D co-operation project has evolved between CEERI and University Catholique de Louvain, Belgium, as a direct result of interaction between these two organisation Oring the course of the UNDP project details of which have appeared earlier in this report. Under this project, advanced microchips for industrial and Power control applica tions would be developed jointly. Based on the expertise gained development of Silicon gate NMOS technology and a certain level of infrastructural facilities available at CEERI, Deptt. of Electronics (Govt. of India) has started funding a project on the development of -"Multilevel Interconnect Technology for VISI' at CEERI.

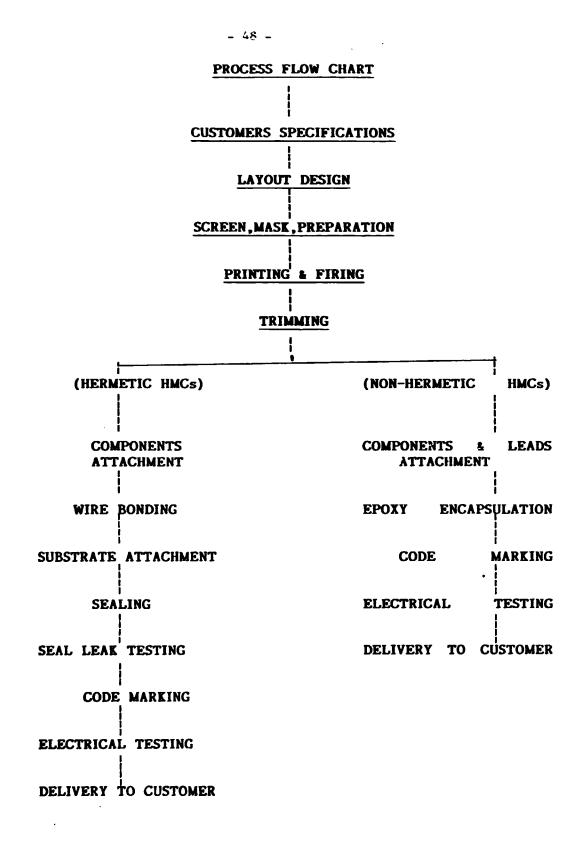

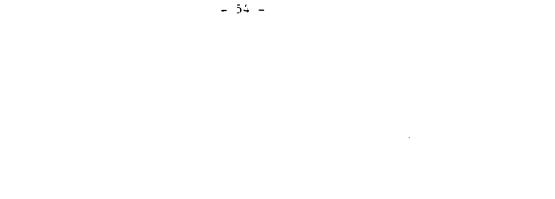

#### C. DEVELOPMENT OF HYBRID CIRCUIT MODULES:

#### xix) SUMMARY

The increased usage of electronics in Control Systems makes reliability of electronic circuits a major concern. Recognising the importance of Hybrid Micro Circuit (HMC) Technology over PCB technology in terms of reliability, size, performance, weight etc., two different types of Base drive HMCs to drive 100 Amp. transistors & 300 Amp. transistors have been developed. Both these HMCs have met the electrical specifications provided by the Power Electronics Laboratory of the Institute. To accomplish this task computer programmes for resistor design and for calculating hybrid package to junction temperature rise have also been developed and successfully used. Power Resistors and Power conductors were designed, fabricated and evaluated. The data generated by these experiments was used in the design of Power HMCs. As a by-product Power Resistors (3 ohms, 15 watts) were fabricated, to help the systems group. These have been used by them in the inverter system.

#### xx) Design Considerations

a) In any hybrid ciruit design, component attachment techniques, package materials and circuit layout are all significant variables effecting the cost and operation of the finished product. When designing high power hybrid circuits, these variables become even more critical.

- 47 -

FIG.C1

Fig. C2A and C2B

Depending upon the user requirements, materials, components, type of package, process etc. can be selected. For Base Drive circuit, being a power hybrid, alumina substrate, and aluminium and copper packages have been selected.

Before actual design of the layout, study of resistor test pattern and coductor test pattern was carried out.

#### b) Resistor Test Pattern (Power)

A resistor test pattern (shown in Fig. 2A) having six numbers of resistors (resistance value 1 ohm) was designed and fabricated on  $3" \times 1" \times 0.005"$  alumina substrate. Measurement were taken on a set of eighteen resistors. Hot temperature coefficient of resistance, Noise index, power handling capacity and thermal storage at 150 C for a period of 2000 hrs were studied. The results are summarised as follows:

- 1. Hot TCR 50 ppm/ C

- 2. Noise Index 7 db

- 3. % change of resistance after 200 hrs at 150 C 0.5%

- 4. Power handling capacity 100 watt/inch

#### c) Conductor Test Pattern (Power)

A conductor test pattern (shown in Fig. 2B) having different width 1 mm to 7 mm of Pd/Ag conductor was designed and fabricated on 2" x 1" C 0.025" alumina substrate. Sheet resistance was found to be 25 m ohm/sg. Current capacity of 1 mm line was found to be 1000 ma. In order to increase the current capacity, solder cream was printed on 1 mm line and then reflowed. After reflow of the solder, sheet resistace came down to 2.5 m ohm/sg. It was

- 50 -

further reduced to 1.2 m ohm/sq. by multiple printing & reflowing the solder cream.

#### xxi) Layout

Considering size of components like transistors, diodes and capacitors, layout pattern was designed on a graph sheet. Resistor dimensions were calculated using a computer program, developed by the group.

In the present HMCs developed at CEERI, add-on components like transistors, diodes, capacitors, and ICs are soldered on thick film pattern. Case of the power transistor being surface mount type, is soldered on to substrate. SIL type leads are clipped on the substrate edge and dip soldered. Then this assembly is mounted on a aluminium and or copper plate using thermally conducting epoxy. Selection of components, leads and package is given in section xxiii.

#### xxii) Thermal Design

A computer program in PASCAL for computing Hybrid case to junction temperature has been developed. Calculating the hybrid case to junction rise for various transistors and other components actual temperature of the hybrid case can be predicted.

#### xxiii). Componets & Their Placement technique

Transistors, diodes and ICs are available in semicoductor chip, micro-packaged and normally packaged forms.

For these types of circuits the ideal design is to use surface mounted devices (SMD). Extensive literature survey was done. It was found that all the devices are at present not available in SMD form. Only 10 devices out of 15 devices used in the circuits are commercially available as SMD. The manufacturers/small quantity suppliers were requested to supply However, SMD's come in packaged tapes/reels containing them. 100,500,1000 devices per reel. Hence no one even quoted for them inspite of our several reminders. It was, therefore, decided to use normally packaged and SOT semiconductor components due to their availability. In our design of the HMC, case of high power transistors BD 203, BD 137 and BD 138 was flatly mounted on to Pd/Ag conductor pad using solder material. Their leads were bent in a special manner so that these could be attached to the required pads. While designing the layout, bonding pads of the case of all the transistors were kept away from other circuit elements in order to minimise their heating effects on other components. Other low power components like opto coupler were mounted above the resistors as they do not dissipate any appreciable power. High power resistors were also spaced well in order to avoid their heating effects to other components. All the add-on components (transistors, ICs, diodes and chip capacitors) were soldered in a single reflow cycle, i.e., by printing of solder cream, placement of components and reflow technique.

- 52 -

### xxiv). Leads

During design of the HMCs layout, all the input/output and other connection pads were kept in one line so that single in line type of leads could be available to the user for direct soldering of input/output wires.

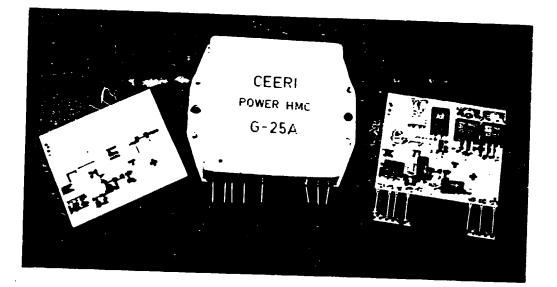

#### xxv) Package

Special type of packages were designed and fabricated so that they could meet the environmental conditions, power handling capacity, protection to components integrated on alumina substrate etc. Aluminium and copper materials for packages were selected because of their good thermal conductivity, availability and cost etc. These packages can be rigidly mounted on the desired place with the help of two screws.

Hybrid versions of Base driver circuit for 100 amp. transistor and 300 amp. transistor are shown in Fig. 3. Mechanical and Electrical data of both of these HMCs are given in Annexure 3 & 4.

È.

Fig.C3 (A) BASE DRIVE HYBRID MICRO CIRCUIT (B) THICK FILM SUBTRATE (C) H.M.C. BEFORE PACKAGING

# BASE DRIVE CIRCUIT FOR 300 AMPERE TRANSISTOR

APPLICATION:

• TO DRIVE THE POWER DARLINGTON WITH ISOLATION (UPTO 300 Amp. Transistor)

•SPECIALLY DEVELOPED FOR ELECTRIC VEHICLES.

FEATURES:

- · SMALL SIZE AND WEIGHT

- COMPACTNESS

- . HIGH RELIABILITY

- GOOD HEAT TRANSFER

- · EASY MOUNTING

- · CIRCUIT SECRECY

SPECIFICATIONS:

(A) Electrical:

(1) OPERATING VOLTAGE + 8V (2) OUTPUT POWER 29 WATT (Approx.)

B) Mechanical:

High Power Resistors for Inverter

D. <u>DEVELOPMENT OF SOLID STATE AC MOTOR DRIVE AND SYSTEM PACKAGES</u> xxvi) <u>Objective</u>

The main objective of the project is to promote the utilization of power electronics systems for decreasing the production costs and increasing the operational efficiency of electric vehicle drives. This objective has gained further importance due to the recent crisis and price rise in fossil fuels. Electronic control systems for future electric vehicles will be mostly based on either AC motor control with inverters or DC motor control with choppers. Although the modern DC traction motor has been developed to a high degree of sophistications; offers the AC motor many advantages, particularly for battery operated vehicles.

xxvii) CEERI Power Electronics Group, therefore, identified the "development of an efficient AC Induction motor drive for transportation applications" as the immediate project aim.

This was subdivided into following main tasks:

- (a) Study and analysis of Pulse Width Modulated (PWM) signal/waveform with respect to losses in motor due to harmonic contents and switching losses in inverter.

- (b) Design and development of Microprocessor based PWM logic and control system.

- (c) Study of various feed back control schemes to-select suitable control strategy for electric vehicles.

- (d) Design and development of Microprocessor based feedback control system.

- 57 -

- 58 -

- (e) Design and development of 20 KVA Transistor inverter using 300 Amp. transistors.

- (f) Testing of 20 KVA transistor inverter with microprocessor based PWM logic.

- (g) Testing of 20 KVA transistor inverter alongwith microprocessor based PWM logic, feedback control system and motor as AC motor drive.

- (h) Simulation of Inverter driven induction motor for adaptive control applications.

# xxviii) Design & Development

(i) Detailed theoretical analysis on harmonic distortion for the following PWM techniques was completed so as to choose the best PWM technique which gives minimum lower order harmonics.

ŧ

- (a) Natural sampling technique

- (b) Symmetric regular sampling technique

- (c) . Asymmetric regular sampling technique

- (d) Modified asymmetric regular sampling technique (suggested by CEERI)

- (e) Area method (suggested by CEERI)

- (f) Modified area method (suggested by CEERI). Measurement of harmonic distortion was carried out on 40 KVA PWM inverter (please see photograph) in order to support the theory with practical observations.

Fig.D.1 - 40 KVA PWM Inverter for AC Motor Drive

- (j) A general purpose microprocessor based pulse width modulated logic was designed and developed. The speciality of this microprocessor based system is its flexibility to handle the following PWM techniques with suitable (minor) changes in the software :

- (a) Symmetric regular sampling

- (b) Asymmetric regular sampling

- (c) Modified asymmetric regular sampling

- 'd) Area method, and

- (e) Modified area method.

- xxix) In order to achieve the required torque speed characteristics of induction motor to suit transportation applications necessary feedback control is needed. A detailed study of various feedback control schemes was undertaken. Two new feedback control techniques namely "Air gap flux control using reactive power measurement" and "Rotor Slot Method" were developed. The first technique is implemented using 68000 microprocessor in the present AC motor drive developed under UNDP.

- XXX) The inverter controls the power supplied to the load by using the logic signals generated by PWM control logic using 300 Amp. transistors. A transistor inverter as shown in photograph 2 as switches with following special features was designed, developed and tested:

- (a) Compact fabrication to minimise lead inductances

- (b) Use of switched mode power supplies (SMPS) for logic and base drive circuits to improve the efficiency and decrease the size.

- (c) Base drive circuits with interlocking facility to protect from 'shoot through' in the inverter.

- (d) Use of non-inductive shunt to measure the dc input current for protection.

- xxxi) The transistor inverter using 100 Amp. transistors was tested at 50 Hz in six step mode and Table-1 shows the observations regarding the power handling capacity of the inverter.

- xxxii)The transistor inverter using 300 Amps transistors was tested and Table-2 shows the observations from 10 Hz to 30 Hz with microprocessor based PWM logic in open loop condition. 30 Hz is

Fig. D.2 - AMP Transistor Inverter

the base frequency of the AC drive where maximum power is consumed. Photograph 3 shows the complete test setup of the AC motor drive with microprocessor based PWM logic, feedback logic, transistor inverter and motor.

<u>TABLE -1</u>

| S.N. Vớc |              | Idc | freq. RPM |     | VAC IAC<br>(RMS) (RMS) |        | VDC  | IDC  |  |

|----------|--------------|-----|-----------|-----|------------------------|--------|------|------|--|

| 1.       | 100V         | 15A | 10 Hz     | 277 | 11.2v                  | 41.00A | 24 V | 8A   |  |

| 2        | 100V         | 30A | 15 Hz     | 415 | 17.1V                  | 58.75A | 40 V | 24 A |  |

| 3.       | 100V         | 50A | 20 Hz     | 553 | 23.2V                  | 76.25A | 55 V | 33 A |  |

| 4.       | 100 <b>V</b> | 72A | 25 Hz     | 686 | 29.3V                  | 98.75A | 70 V | 42 A |  |

| 5.       | 100V         | 90A | 30 Hz     | 850 | 42.6V                  | 75.00A | 80 V | 50 A |  |

$\underline{\text{TABLE}} = \underline{2}$

| Edc | (v) Idc | (a) Pdc (w) | VAC (v) | IAC (A) | PAC<br>Motor<br>VA | Slip  | VG (v) | IG(A) | PG (W) |

|-----|---------|-------------|---------|---------|--------------------|-------|--------|-------|--------|

| 80  | 20      | 1600        | 67      | 25      | 2901               | 0.49  | 0      | 0     | 0      |

| 80  | 30      | 2400        | 67      | 29.25   | 3395               | 0.603 | 30     | 20    | 600    |

| 80  | 180     | 14400       | 62.4    | 120     | 12969              | 2.38  | 120    | 60    | 7800   |

| 00  | 254     | 25400       | 77.5    | 165.25  | 2215               | 2.54  | 180V   | 61    | 11078  |

Fig.D.3 - Total Test Set up for 300 Amp. Transistor Inverter

- xxxiii)The transistor inverter using 300 Amp. transistors with microprocessor based PWM logic and feedback control logic is presently under test.

- xxxiv)The activity on simulation of inverter fed induction motor was carried out at University of Wisconsin and results were used in developing the PWM transistor inverter.

- xxxv) The following activities were undertaken to provide necessary design inputs to the semiconductor device group.

- (a) complete specifications were prepared for three VLSI chips namely "VME BUS COMPATIBLE CHIP", (Chip 1),

"PWM Chip 2" and "PWM Chip 3" in consultation with VLSI group.

- (b) Two base drive circuits one for 100 Amp.and other for 300 Amp.transistors was designed and developed. The designs were provided to Hybrid microcircuits group for fabrication.

- (c) Tested a batch of 100 Amps.transistors, developed by CEERI alongwith CEERI HMC group developed base drive circuit. Fig. 4 shows the test set up for the same.

- (d) Preliminary testing of PWM 1 and 2 chips and VME bus compatible chip, was completed.

- (e) Design and fabrication of ADC card using VME bus compatible chip is in progress.

- (f) Tested Hybrid base drive circuits for 100 Amp.and 300 Amp.transistors.

Fig. D.4 - Test Set Up for CEERI Made Transistor

The objective mentioned in the section 2 are achieved. The other hard and soft outputs are as follows:

XXXVII) OUTPUTS

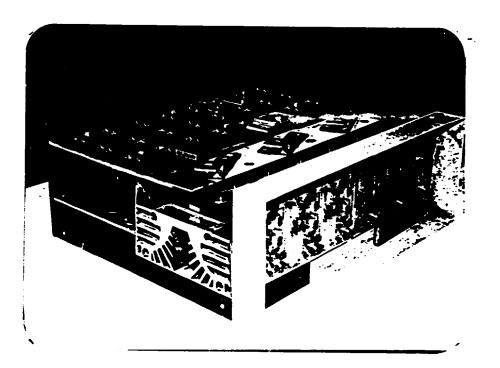

A total system package for 20 KVA transistor inverter suitable for transportation applications consisting of the following modules was developed.

- (a) A system package for microprocessor based pulse width modulation (PWM) logic.

- (b) A system package for microprocessor based feedback logic

- (c) 20 KVA transistor inverter using 300 Amp.transistors

(photograph 2)

- (d) Improved model of 300 Amp. transistor inverter, partially engineered (photograph 5)

- (e) Prototype model of transistor inverter using CEERI100 Amp.transistors (Photograph 6).

- (f) A single phase to three phase converter was developed using 100 AMp. power transistor (CEERI make) to use with irrigation pumps for rural applications.

- (g) 300 watt. SMPS (Switched Mod. Power Supply) with 24 V DC (Battery) input for material movement application in industry.

Established the basic infrastructure and facilities to undertake power electronics project upto 200 KVA power level.

Fig.D.5 - 300 Amp Transistor Inverter : Engineering Model

Fig. D.6 - CEERI, 100 Amp Transistor Inverter

.

# xxxviii) Bottlenecks faced and remedial measures taken:

- a) The main problem was of procurement of components in time especially the power transistors. This was solved with the help of UNDP experts, consultants and their contacts but the transistors indented through UNDP could not be procured till date. Only a few pieces were received by end of 1987.

- b) The second main problem was the operation of inverter on full voltage. This was initially not possible due to voltage spike at the collector of the transistor due to stray inductances. This problem was solved by employing a new approach to fabricate the power module.

- c) A need for the protection of the power devices of inverters under abnormal condition was felt. A simple and cheaper noninductive shunt (fabricated in CEERI) is used to measure the d.c. input current for the protection of the system.

OUTPUTS

16. From the foregoing it is seen that the outputs as listed in the project document have been completed execpt a few which are likely to be completed in the near future. The delay has been due to external factors as mentioned in the previous paragraphs.

- 71 -

The details of these out puts is as given below:

- (i) <u>Batches of Power transistors for power control in</u> electric drives for transportation.

- a) Darlington Transistor 100 Amp.

A batch of about 17 Nos. of 100 Amps. Darlington transistors have been delivered to the systems group. These transistors meet the specifications required for the Transportation applications, particularly low power inverter drives. These transistors have been used in CEERI make Inverter to drive A.C.motor. These devices have successfully worked for Single Phase and Three Phase A.C. drive system.

On account of this successful achievement BHEL have rdered for large No. of Darlington Transistors to be used by BHEL, Bhopal.

b) Darlington Transistor 300 Amps.

The design for this transistor have been completed and P.G. tape is ready. Further processing is in progress.

### (ii) <u>Batches</u> of <u>custom</u> <u>design</u> <u>Monolithic</u> <u>integrated</u> <u>circuits</u> for <u>PWM</u> drives for use in transportation.

- a) <u>Chip No. 1</u>: VME Bus compatible controller chip for Multichannel analogue data acquisition, successfully designed and tested 12 Pieces have been fabricated.

- b) <u>Chip No. 2</u>: Design of the PWM processor data path chip successfully completed and validated through the testing of fabricated chips.

- c) <u>Chip No. 3</u>: Design of the PWM processor controller chip debugged through testing of the fabricated chip. Design modifications completed and refabrication initiated.

In the original project document only design and fabrication of a batch of chip 1 was envisaged. After the visit of Prof. Jespers from UCL Belgium, the design of more complex chips (chip 2 - 7500 components and chip 3 3000 components) were thought of as Professor Jespers agreed to provide CAD and chip fabrication facilities.

Chip 2 had a fault in the mask fabrication and chip 3 had design fault. These faults have been rectified. The processing is being done in Belgium for chip 2 & 3 and also simultaneously for chip 3 at Pilani. It is hoped that by Nov/Dec 1988 the good fabricated chips would become available.

One batch of fabricated wafers from UCL, Belgium for the PWM data path and the modified PWM controller design have been received. The design modification was achieved during the UNDP fellowship training of Dr. Mrs. Srivastava and the wafer fabrication was achieved durin g the UNDP fellowship training of Dr. V.K.Dwivedi. The parameter and functional testing on the wafers is to be completed.

A batch of modified PWM controller design whose masks were made inhouse at CEERI is at the final stages of fabrication at CEERI. Resulting chips will be tested along with the chips received from UCL, Belgium.

iii) <u>Batches of hybrid Integrated Modules for control of Electric</u> drive for transportation.

Base drive circuit for 100 Amp. (5 pieces) and 300 Amp. (11 pieces) transistor have been developed. Both these circuits have been tested by the system group and meet the specifications. These circuits have been delivered in batches of circuits.

iv) <u>Prototype of solid state AC drive and system modules for</u> transportation applications.

A prototype of 20 KVA transistor inverter using 300A transistor has been designed, fabricated and tested.

v) <u>Technical report on the development of 100 Amp Darlington</u> <u>Transistor.</u>

Completed.

b) <u>Technical report on the development of 300 Amp.</u> Darlington transistor

under preparation

- 73 -

C) MoS IC development.

> i) Report for the design and development of chip 1 Completed

- 74 -

- ii) Report for the design and development of chip 2 & 3. Completed.

- d) Report on Hybrid Integrated Module Development. Completed.

- e) Technical report on development of 40 KVA AC drive. Completed

- **f**) Technical report on development of 300 Amp. transistor inverter.

Completed.

Video tapes of lectures (15 Nos.) vi)

Ready.

#### Conclusions

Outputs as envisaged in the project documents have been achieved except the fabrication of 300 Amp. transistor which is in progress. Additional outputs, i.e., fabrication of chip-2 and Chip-3 were fabricated and there are being reprocessed at UCL Belgium and are likely to be completed by Nov./Dec. 1988.

Taking note of the above it can be stated that about 90% of the envisaged outputs have been completed and further additional outputs Chip-2 and Chip-3, are at the advanced stage of  $d \in very$ .

- 75 -

#### IV. ACHIEVEMENT OF OBJECTIVES

- 17. The Power Transistors are being manufactured by a few companies, in the world. These companies are selling system modules and not the transistors. And under such situation the development of capability for the development and manufacture of Power Transistors has been well recognised by leading manufactures of systems in India (BHEL) and planners. BHEL provided excellent facilities, almost all required to package the 100 Amp. transistor. The developed device has met all specifications and passed reliability tests as desired by System Group. BHEI. Bangalore and Bhopal have matched the progress towards this direction. Now BHEL Bhopal has already orered for large number of transistors, match would be produced at BHEL Bangalore, with the consultancy of CEERI.

- 18. The approach of the project to develop Application Specific Integrated Circuits (ASICs) for performing the brain functions of the systems have been accepted world wide and the production of ASICs is increasing in the world market. In India the largest manufacturer of Integrated Circuits, the Semiconductor Complex Limited has also oriented its production program for the development & manufacture of ASICs.

- 19. The Hybrid Circuits are known for their reliability and the manufacturers of systems have started using them in larger numbers. A number of companies have started manufacturing Hybrid Circuits in India. One of them M/s Minicircuits Pvt. Ltd., Bangalore has been set up in collaboration with CEERI. A couple of more companies are contemplating know-how from this Institute.

- 76 -

- 20. There is now complete awareness that the Electronics Systems using AC Drives for transportation are cheaper, efficient and reliable. These systems reduce the consumption of energy and are well suited for fast energy sources depicting situations and reduction in environmental polution.

#### V. UTILIZATION OF PROJECT RESULTS

#### (1) Power Transistors

- 21. The expertised developed in the project has been used to design and develop fast switching Power Thyristor for BHEL. Specifications 1700V, 13003, with 40 microsecond switching tune.

- 22. The interaction with BHEL has been developed to such an extent that the development of transistors (wafer processing and packaging) has been done at BHEL, almost free of cost.

- 23. The silicon gate NMOS technology developed, has been used to fabricate other circuits (e.g. a custom chip for microprocessor controlled 32-line PABX).

- 24. Samples of the VME-bus compatible controller chip for multichannel analog data acquisition have been given to in-house system designers for building prototype systems.

A dialogue has been initiated with SCL, Chandigarh for assessing the possibility of their productionising this design or a OMOS version of it at Chandigarh.

- 25. Two industrial units (BHEL, L&T) as well as some academic organisations have shown interest and requested for the samples of the PWM processor chips.

- (2) Hybrid Microcircuits

- 26. One factory M/s. Minicircuits Private Limited, Bangalore has been setup with the know-how and consultancy from CEERI. This

factory is likely to achieve a turnover of Rs. 20 million during this financial year.

- 27. Indian Space Research Organization(ISRO) has recognised CEERI as the only supplier of space qualified Hybrid Microcircuits.

- (3) Electronic Systems

- 28. The system group developed a prototype transistorised power supply system for ICED LIN REFRIGERATOR (ILR) to be used in Immunization Programme under National Health Programme supported by WHO, using the inverter fabrication techniques developed during UNDP Programme.

- 29. BHEL has recently shown interest in utilizing the Know-how of 20 KVA transistorised inverter developed by CEERI under UNDP project for their electric vehicle programme.

- 30. Considering the expertise gained and capability developed by CEERI under UNDP project, CSIR is proposing to design and develop "SOLAR POWERED CAR" which will use most of the UNDP project outputs directly or indirectly.

- 30A. The 40 KVA PWM Inverter for Mining Locomotive has been identified by BHEL.

- VI. FINDINGS